### Dependability Driven System Level Co-Design and Optimization of Embedded Systems

Vom Fachbereich Informatik der Technischen Universität Darmstadt genehmigte

Dissertation

zur Erlangung des akademischen Grades eines Doktor-Ingenieur (Dr.-Ing.)

vorgelegt von

### Md. Shariful Islam

aus Bangladesch

Referenten: Prof. Neeraj Suri, Ph.D. Prof. András Pataricza, Ph.D.

Datum der Einreichung: 16.10.2008 Datum der mündlichen Prüfung: 10.12.2008

> Darmstadt 2008 D17

### Executive Summary

Embedded systems are becoming pervasive in diverse application domains such as automotive, avionic, medical, control and their functionality is increasingly defined by software (SW). Such systems especially in safety-critical (SC) applications, with implications on system *dependability* and *real-time* must be designed to be dependable (fault tolerant) enough and have to meet timing requirements in order to avoid any potential catastrophic consequences. More and more new and innovative functionality is being integrated into such systems, invariably leading to a heterogeneous environment consisting of applications of *mixed-criticality* (SC and non-SC), each with associated extra-functional requirements such as *dependability, timing, resources* and *power consumption*. Efficient system design methods and techniques are needed to be developed to integrate these diverse applications across limited hardware (HW) resources.

This thesis develops a novel dependability-driven system level SW-HW co-design methodology which systematically guides the design and optimization of such embedded systems from requirements analysis phase through integration to the prototyping. We first develop the concept of a consolidated mapping of SC and non-SC applications onto a common distributed computing architecture such that their operational delineation is maintained over the integration. We then devise an optimization based co-design approach through quantifying the various design objectives/variables. Our aim is to develop the design methodology for an integrated embedded architecture.

A heuristic based systematic mapping process is elaborated for integrating varied criticality applications. A set of functional and extra-functional *requirements* and *constraints* are satisfied during the mapping. At an early design stage, the mapping considers rigorous design strategies such as *fault tolerance, fault/error containment, robust partitioning, timeliness, resource* and *power consumption*. Dependability is ensured through replication of application jobs with high criticality and a schedulability analysis is presented for guaranteeing the timeliness properties. The developed mapping algorithm generates an initial feasible solution and guides the optimization in a unified and efficient way.

We develop a comprehensive multi variable optimization (MVO) framework which *quantifies* and *optimizes* a set of competing variables from dependability, real-time and resource perspectives. During the optimization process the satisfaction of constraints is maintained. The key aspect of the approach is to enhance dependability by using fault containment mechanisms including the quantification and estimation of the considered design variables. The framework is extended by quantifying and modeling the reliability and system level power consumption as design variables.

In order to evaluate and validate the developed methods and techniques presented in the thesis, we have performed extensive experiments. Throughout the thesis we illustrate our ideas and concept using real-life automotive examples (where these techniques were actually validated). The concept is applied to a supporting tool set where we develop a prototype of the system level co-design approach. The prototype is created adhering to a *transformation based design* process.

## Kurzfassung

Eingebettete Systeme sind in allen Bereichen der Automobil-, Avionikund Kontrollanwendungen gegenwärtig und werden zunehmend durch Software (SW) definiert. Solche Systeme mit direkter Auswirkung auf die Zuverlässigkeit und Echtzeit müssen zuverlässig (fehlertolerant) genug sein und strenge Echtzeitanforderungen erfüllen um mögliche katastrophale Folgen wie den Verlust von Menschenleben, Schaden für die Umwelt oder den Verlust von Eigenschaften zu vermeiden. Die Integration von vielen neuen und innovativen Funktionalitten in solche Systeme führt unweigerlich zu heterogenen Umgebungen, bestehend aus sicherheitskritischen als auch nichtsicherheitskritischen Anwendungen (mixed-criticality), jeweils mit den damit verbundenen extrafunktionalen Anforderungen bezüglich Zuverlässigkeit, Echtzeit und Ressourcen. Effiziente System-Entwurfsmethoden und Techniken sind erforderlich, solch unterschiedliche Anwendungen in begrenzten Hardware (HW) Ressourcen zu integrieren.

In dieser Dissertation entwickeln wir eine neue, verlässlichkeitsorientierte SW-HW Co-Design-Methode für die Systemebene, die den Entwicklungsprozess und die Optimierung solch eingebetteter Systeme von der Anforderungsanalyse über die Integrationsphase hin zur Realisierung des Prototypen in systematischer Weise führt. Zunächst entwickeln wir das Konzept einer gemeinsamen Abbildung von sicherheitskritischen als auch nicht-sicherheitskritischen Anwendungen auf eine gemeinsame, verteilte Rechnerarchitektur, so dass ihre operative Abgrenzung über die Integration erreicht wird. Weiterhin haben wir durch Quantifizierung der verschiedenen Entwurfsziele und Variablen einen optimierungsbasierten Co-Design-Ansatz erstellt. Unser Ziel ist es eine integrierte, eingebettete Architektur zu entwerfen.

Ein systematischer, auf Heuristiken basierter Abbildungsprozess wird für die Integration von Anwendungen unterschiedlicher Kritikalität entwickelt. Eine Reihe von funktionalen und extra-funktionalen Anforderungen und Randbedingungen sind während des Abbildungsprozesses erfüllt. Schon in der frühen Entwurfsphase berücksichtigt der Abbildungsprozess strenge Designstrategien wie Fehlertoleranz, Fehlereingrenzung, robuste Partitionierung, Echtzeit, Ressourcen- und Energieverbrauch. Zuverlässigkeit wird durch Replikation von Anwendungen mit hoher Kritikalität garantiert, die Echtzeiteigenschaften durch eine Schedulability-Analyse gewährleistet. Der entwickelte Abbildungsalgorithmus generiert zuerst eine zulässige Lösung und führt dann die Optimierung in einheitlicher und effizienter Weise durch.

Ein umfassendes Rahmenwerk für eine Multi-Variablen-Optimierung (MVO) wird entwickelt, das eine Reihe von konkurrierenden Variablen im Hinblick auf Zuverlässigkeit, Echtzeit und Ressourcenverbrauch quantifiziert und optimiert. Während des ganzen Optimierungsprozesses wird die Einhaltung der Randbedingungen garantiert. Der wichtigste Aspekt dieses Konzepts ist die Erhöhung der Zuverlässigkeit durch die Verwendung von Fehlereingrenzungsmechanismen wie Quantifizierung und Abschätzung der betrachteten Design-Variablen. Das Rahmenwerk wird dahingehend erweitert, dass die Zuverlässigkeit des Systems und der Stromverbrauch auf Systemebene als Design-Variablen quantifiziert und modelliert werden. Zur Evaluierung und Validierung der in dieser Dissertation entwickelten Methoden und Techniken werden umfangreiche Experimente durchgeführt. Im gesamten Verlauf der vorliegenden Arbeit, werden unsere Ideen und Konzepte anhand von praxisnahen Beispielen aus der Automobilentwicklung erläutert (wobei der Einsatz dieser Techniken zugleich validiert wird). Das Konzept wird auf eine Sammlung von Werkzeugen angewendet wobei wir einen Prototypen unseres Co-Design Ansatzes für die Systemebene entwickeln. Der Prototyp wird gemäß den Vorgaben eines transformationsbasierten Entwurfsprozesses erstellt.

### Acknowledgements

With great pleasure, I would like to take this opportunity to thank all the people who have supported me in the successful completion of this thesis. At first I would like to express my sincere thanks to my advisor Prof. Neeraj Suri for his excellent supervision, scholastic guidance and constructive suggestions during this four years of working in the DEEDS group. A very special thanks to Prof. András Pataricza for accepting to be my external supervisor.

I am very thankful to all my past and present colleagues including Ute and Sabine in the DEEDS group for their support and for a nice working environment. Some of my research work has been done in collaboration with the EC DECOS project, thanks to several academic and industrial partners for fruitful discussion during the project work. I have got the opportunity to apply my developed concept in practice. I am also very grateful for the financial support from that project.

Last but not least I would like to express my thank to my parents, my wife and my siblings for their support, encouragement and love during this time period.

# Contents

| E            | xecut | tive Su | ımmary                                      | iii  |

|--------------|-------|---------|---------------------------------------------|------|

| K            | urzfa | ssung   |                                             | v    |

| $\mathbf{A}$ | ckno  | wledge  | ements                                      | vii  |

| 1            | Inti  | oduct   | ion                                         | 1    |

|              | 1.1   | Syster  | m Level Design and Challenges               | . 4  |

|              | 1.2   | Deper   | ndability by Design and Optimization        | . 10 |

|              | 1.3   | Proble  | em Statement and Thesis Research Questions  | . 13 |

|              | 1.4   | Thesis  | s Contributions                             | . 17 |

|              | 1.5   | Thesis  | s Organization                              | . 20 |

| <b>2</b>     | Bac   | kgrou   | nd and System Model                         | 23   |

|              | 2.1   | Prelin  | ninaries                                    | . 23 |

|              |       | 2.1.1   | Target Application Domain                   | . 24 |

|              |       | 2.1.2   | System Requirements                         | . 24 |

|              |       | 2.1.3   | Preview of Resource Allocation Problem      | . 27 |

|              |       | 2.1.4   | Metaheuristics in Optimization              | . 28 |

|              | 2.2   | Relate  | ed Research                                 | . 31 |

|              |       | 2.2.1   | System Design and Co-Design                 | . 31 |

|              |       | 2.2.2   | Mapping – Allocation and Scheduling         | . 32 |

|              |       | 2.2.3   | Optimization                                | . 35 |

|              | 2.3   | Syster  | m Architecture and Models                   | . 38 |

|              |       | 2.3.1   | The Architecture Model                      | . 38 |

|              |       | 2.3.2   | The Communication Model                     | . 41 |

|              |       | 2.3.3   | System Level Partitioning                   | . 43 |

|              |       | 2.3.4   | The Application and SW Model                | . 46 |

|              |       | 2.3.5   | The Fault-Model                             | . 50 |

|              |       | 2.3.6   | Functional and Extra-Functional Constraints | . 51 |

| 3        | Sys | tem Le  | evel Co-Design and Optimization Approach 5                                              | 57  |

|----------|-----|---------|-----------------------------------------------------------------------------------------|-----|

|          | 3.1 | Embe    | dded Systems Co-Design Criteria 5                                                       | 68  |

|          |     | 3.1.1   | Satisfaction of Constraints                                                             | 58  |

|          |     | 3.1.2   | Dependability                                                                           | 58  |

|          |     | 3.1.3   | Real-Time                                                                               | 59  |

|          |     | 3.1.4   | Resource and Power Consumption                                                          | 59  |

|          | 3.2 | Co-De   | esign Space Exploration 6                                                               | 60  |

|          | 3.3 | Const   | raints Handling $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 60  |

|          | 3.4 | Mathe   | ematical Formulation of the Problem $\ldots \ldots \ldots \ldots \ldots $               | 52  |

|          | 3.5 | The I   | ntegrated Design Framework 6                                                            | 55  |

|          |     | 3.5.1   | The Overall Co-Design Methodology                                                       | 66  |

|          |     | 3.5.2   | Requirements Analysis and Specification 6                                               | 59  |

|          |     | 3.5.3   | SW-HW Mapping                                                                           | 70  |

|          |     | 3.5.4   | System Design Optimization                                                              | 70  |

|          |     | 3.5.5   | Prototyping                                                                             | 71  |

| 4        | Dep | oendab  | oility Driven SW-HW Mapping 7                                                           | 3   |

|          | 4.1 |         |                                                                                         | 74  |

|          |     | 4.1.1   |                                                                                         | 74  |

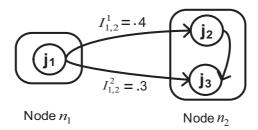

|          |     | 4.1.2   | Influence and Communication Reduction                                                   | 78  |

|          |     | 4.1.3   | Schedulability Analysis                                                                 | 32  |

|          |     | 4.1.4   | Resource Consumption                                                                    | 37  |

|          | 4.2 | Suppo   |                                                                                         | 88  |

|          | 4.3 | Order   | ing Heuristics                                                                          | 39  |

|          |     | 4.3.1   | Job Ordering                                                                            | )1  |

|          |     | 4.3.2   |                                                                                         | 92  |

|          | 4.4 | The N   | Mapping Algorithm                                                                       | )3  |

|          |     | 4.4.1   |                                                                                         | 95  |

|          |     | 4.4.2   | Constraints Satisfaction Technique                                                      | 96  |

|          |     | 4.4.3   | Remarks                                                                                 | 97  |

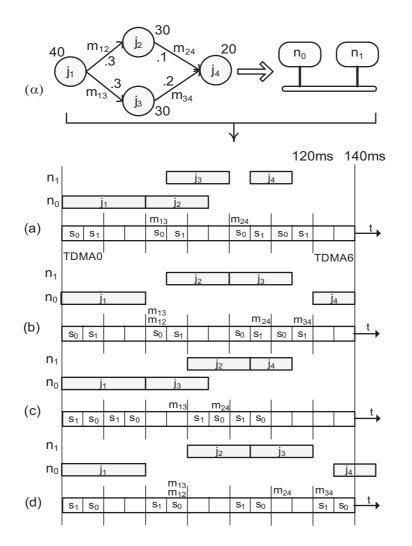

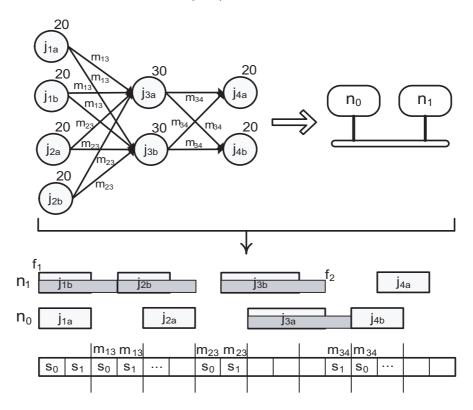

|          | 4.5 | Mapp    | ing Illustration                                                                        | 97  |

|          |     | 4.5.1   | HW Resources and Applications                                                           | )8  |

|          |     | 4.5.2   | Illustration of Mapping Phases                                                          | )() |

| <b>5</b> | Mu  | lti Var | viable Optimization (MVO) 10                                                            | 5   |

|          | 5.1 |         | tial Issues in MVO                                                                      |     |

|          |     | 5.1.1   | General Optimization Ideas                                                              |     |

|          |     | 5.1.2   | Properties of Co-Design Variables                                                       |     |

|          |     | 5.1.3   | Quantifiers of Variables                                                                |     |

|          |     | 5.1.4   | Integration Trade-Offs and Preferential Independence . 11                               |     |

|          |     | 5.1.5   | The Chosen Co-Design Optimization Variables 11                                          |     |

|   | 5.2            | Quantification of Optimization Variables                                                                                                                           |

|---|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                | 5.2.1 Influence                                                                                                                                                    |

|   |                | 5.2.2 Slack and Scheduling Length                                                                                                                                  |

|   |                | 5.2.3 Bandwidth $\ldots \ldots \ldots$             |

|   |                | 5.2.4 Example Describing the Metrics                                                                                                                               |

|   | 5.3            | Our MVO–SA Approach                                                                                                                                                |

|   |                | 5.3.1 The MVO Function                                                                                                                                             |

|   |                | 5.3.2 The MVO Algorithm – Application of SA                                                                                                                        |

|   |                | 5.3.3 The Transformation Operator                                                                                                                                  |

|   |                | 5.3.4 Comparing the Mapping $\ldots \ldots \ldots$ |

| 6 | Eva            | luation 122                                                                                                                                                        |

|   | 6.1            | Experimental Setup                                                                                                                                                 |

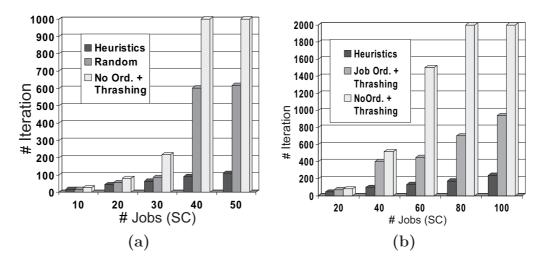

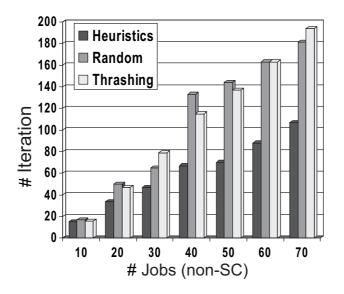

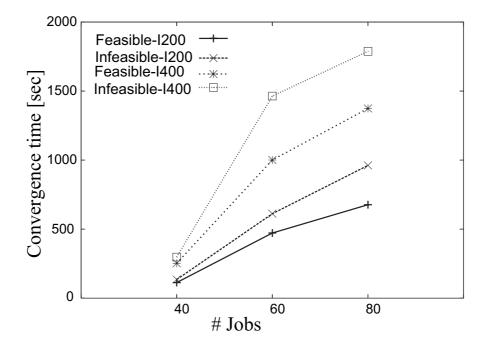

|   | 6.2            | Performance Evaluation of the Mapping                                                                                                                              |

|   |                | 6.2.1 Effectiveness                                                                                                                                                |

|   |                | 6.2.2 Remarks                                                                                                                                                      |

|   | 6.3            | Empirical Evaluation of the MVO-SA                                                                                                                                 |

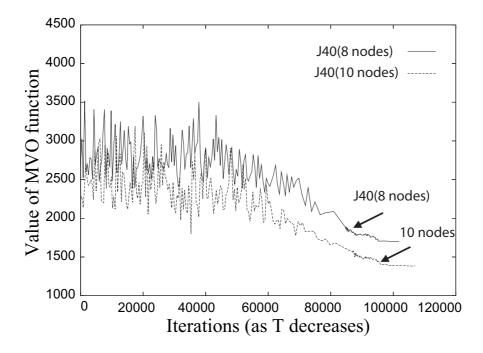

|   |                | 6.3.1 Proof of Convergence and Effectiveness                                                                                                                       |

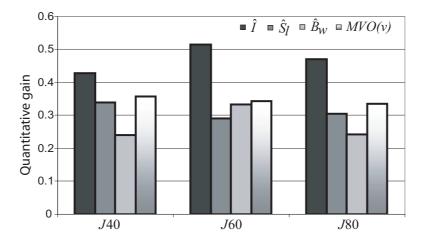

|   |                | 6.3.2 Quantitative Gain                                                                                                                                            |

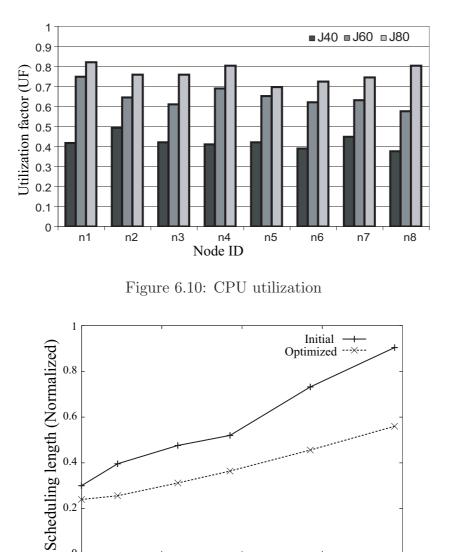

|   |                | 6.3.3 CPU Utilization                                                                                                                                              |

|   |                | 6.3.4 Reduction of FT Overhead                                                                                                                                     |

|   | 6.4            | Validation and Comparative Study                                                                                                                                   |

| 7 | Pro            | totype of the System Level Co-Design 141                                                                                                                           |

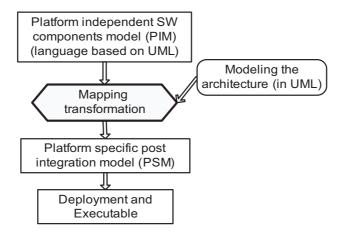

|   | 7.1            | Transformation Based Design                                                                                                                                        |

|   |                | 7.1.1 MDD and PBD: Overview & Relevance                                                                                                                            |

|   |                | 7.1.2 Model Transformation                                                                                                                                         |

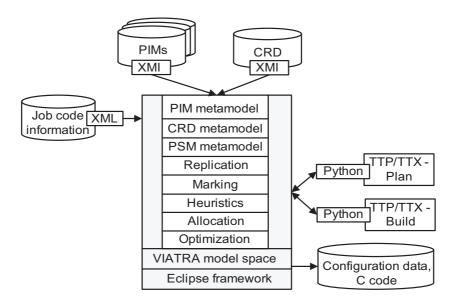

|   | 7.2            | Architecture of the Prototype                                                                                                                                      |

|   |                | 7.2.1 Modeling the Application and SW Development 14'                                                                                                              |

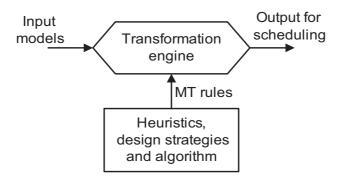

|   |                | 7.2.2 Transforming the Design Steps                                                                                                                                |

|   |                | 7.2.3 Scheduling Tool Support                                                                                                                                      |

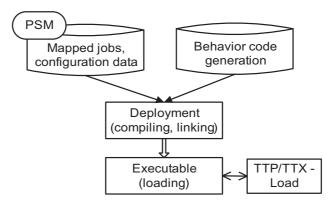

|   |                | 7.2.4 PSM Prototype                                                                                                                                                |

|   | 7.3            | Deployment and Executable                                                                                                                                          |

| 8 | $\mathbf{Ext}$ | endability and Adaptability 153                                                                                                                                    |

|   | 8.1            | Applicability on a Heterogeneous Architecture                                                                                                                      |

|   | 8.2            | Reliability Measure                                                                                                                                                |

|   |                | 8.2.1 Computing Reliability                                                                                                                                        |

|   |                | 8.2.2 Reliability and Mapping Analysis – An Example 158                                                                                                            |

|   | 8.3            | System Level Power Optimization                                                                                                                                    |

|   |                | 8.3.1 Static Power Optimization                                                                                                                                    |

|   |                |                                                                                                                                                                    |

|        | 8.3.2   | Dynamic Power Optimization                             | 161 |

|--------|---------|--------------------------------------------------------|-----|

|        | 8.3.3   | FT and Power Analysis – An Example                     | 163 |

| 9 Cor  | nclusio | ns and Future Issues                                   | 167 |

| 9.1    | The C   | Overall Contributions                                  | 167 |

|        | 9.1.1   | The Integrated Design and Optimization Framework .     | 167 |

|        | 9.1.2   | Consolidated Mapping of Mixed Criticality Applications | 168 |

|        | 9.1.3   | Extra-Functionality Driven Optimization                | 169 |

|        | 9.1.4   | Summarizing the Benefits                               | 171 |

| 9.2    | Future  | e Issues                                               | 172 |

| Biblio | graphy  | ·                                                      | 175 |

| Index  |         | 1                                                      | 193 |

| Curric | ulum V  | Vitae                                                  | 197 |

# List of Figures

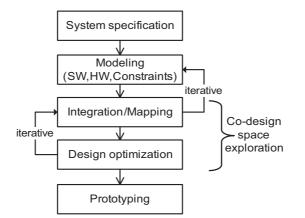

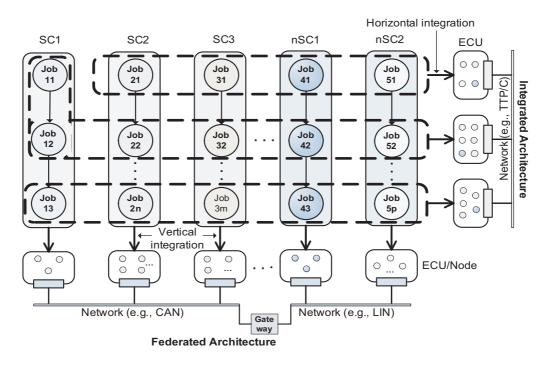

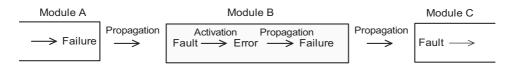

| $1.1 \\ 1.2 \\ 1.3$                                                                                                    | Abstract view of system level design steps5Federated and integrated design approach6The fault, error and failure propagation11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

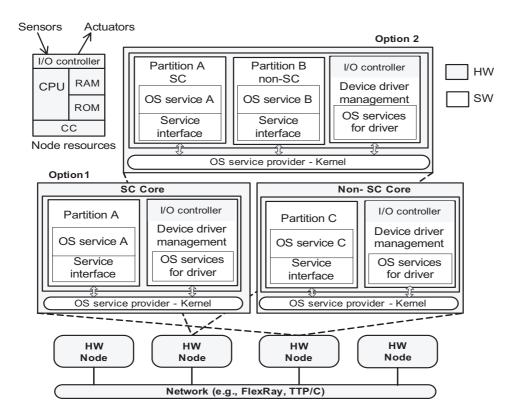

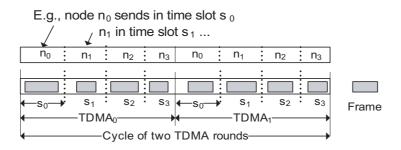

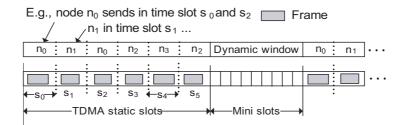

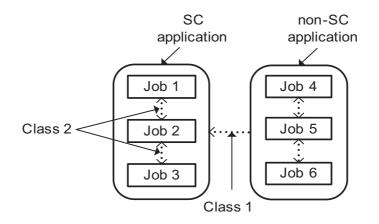

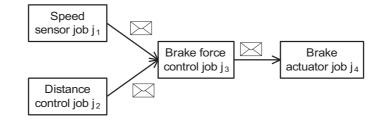

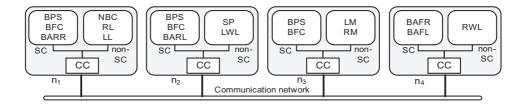

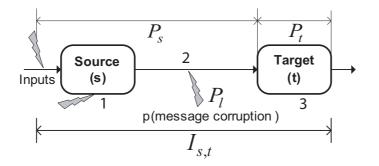

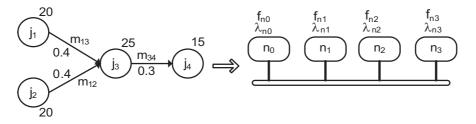

| <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> </ol>                                            | High-level model of the target HW architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

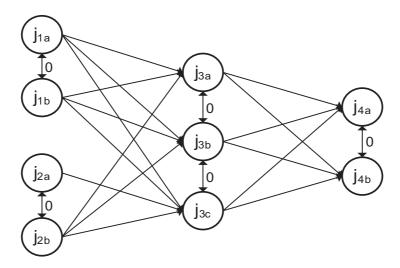

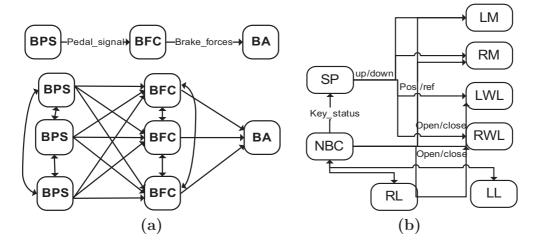

| $2.0 \\ 2.6$                                                                                                           | Brake force control application after replication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

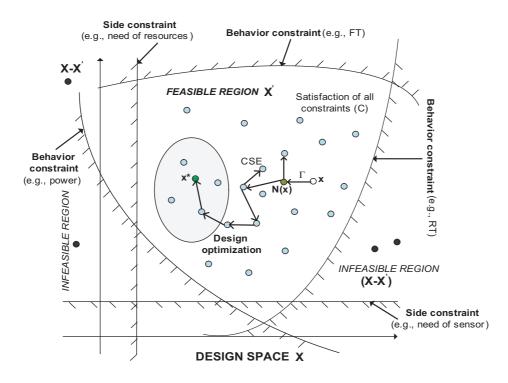

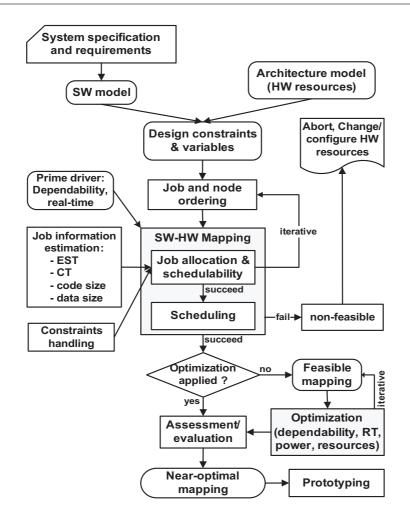

| 3.1<br>3.2                                                                                                             | Hypothetical design space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

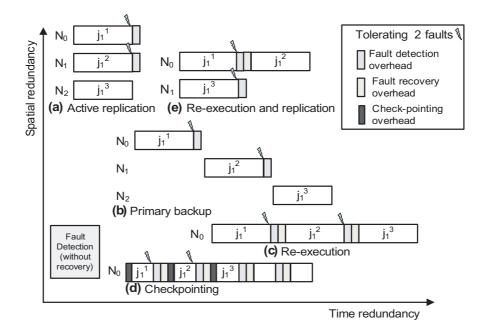

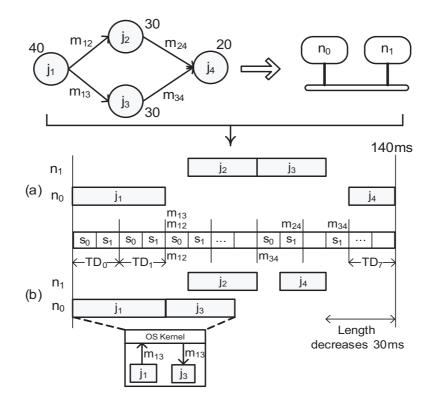

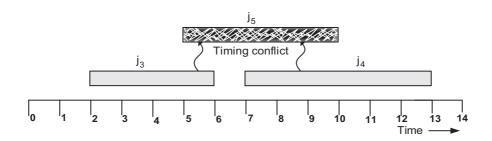

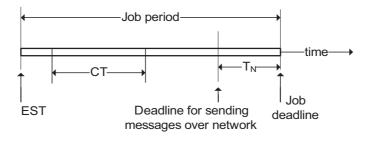

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \end{array}$                                                  | Trade-off between different FT schemes (a)–(e)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

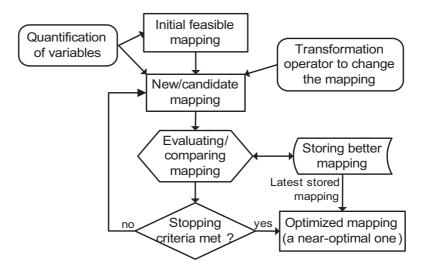

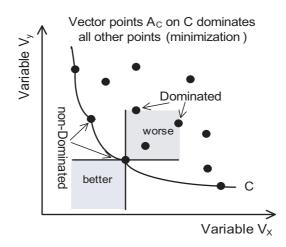

| $5.1 \\ 5.2 \\ 5.3 \\ 5.4 \\ 5.5$                                                                                      | Design optimization flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

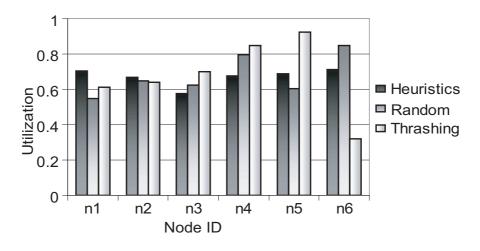

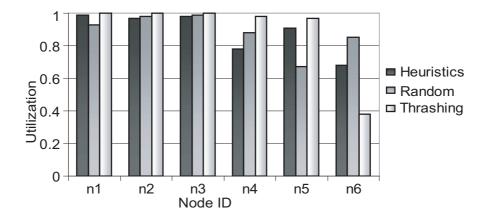

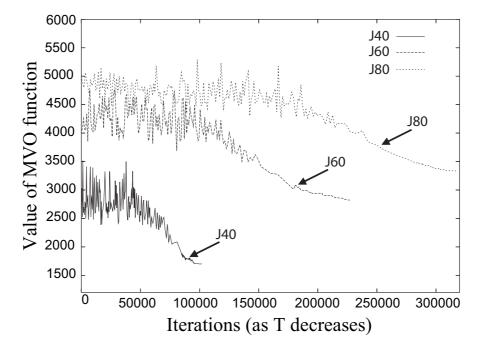

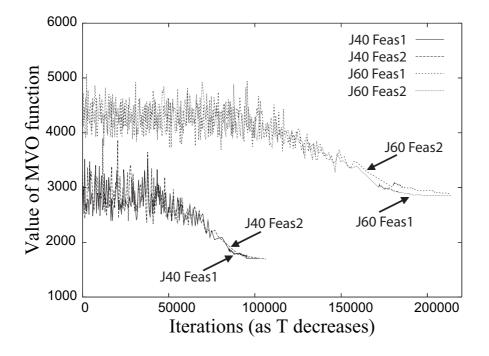

| $     \begin{array}{r}       6.1 \\       6.2 \\       6.3 \\       6.4 \\       6.5 \\       6.6 \\     \end{array} $ | Performance of mapping heuristics (SC applications) 130<br>Performance of mapping heuristics (non-SC applications) 131<br>CPU utilization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0.0                                                                                                                    | $\mathbf{I} \in \mathbf{I} \cup \mathbf{I} = \mathbf{I} \cup $ |

| 6.7  | Effect of adding resources (laxation of constraints) |

|------|------------------------------------------------------|

| 6.8  | Run time comparison                                  |

| 6.9  | Mapping performance profile $M_{PF}$                 |

| 6.10 | CPU utilization                                      |

| 6.11 | Reduction of replication overhead                    |

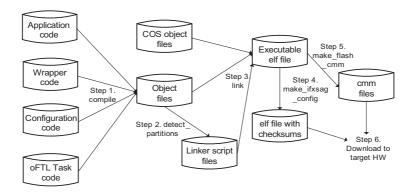

| 7.1  | Transformation based design                          |

| 7.2  | Prototype of the system level co-design              |

| 7.3  | Allocation in model transformation                   |

| 7.4  | Deployment process                                   |

| 7.5  | Deployment steps $[174]$                             |

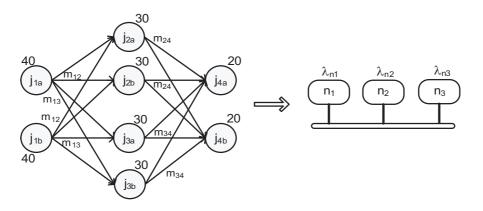

| 8.1  | Application and heterogeneous architecture           |

| 8.2  | Assignment on a heterogeneous architecture           |

| 8.3  | Application and architecture model                   |

| 8.4  | Example mapping - FT and power analysis              |

# List of Tables

| 2.1  | Safety integrity levels                                                                                                                                                     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1  | Building assignment compatibility matrix                                                                                                                                    |

| 4.2  | Building communication matrix                                                                                                                                               |

| 4.3  | Chosen values of job properties (brake-by-wire system) 99                                                                                                                   |

| 4.4  | Chosen values of job properties (doors application) 100                                                                                                                     |

| 4.5  | The sub-matrix $\widetilde{C}$ used in <i>Phase 2</i>                                                                                                                       |

| 4.6  | Jobs allocation of the brake-by-wire application 102                                                                                                                        |

| 4.7  | Building matrix $\widetilde{A}$ for doors control application                                                                                                               |

| 4.8  | The sub-matrix $\tilde{C}$ used in Phase 3 $\ldots \ldots $ |

| 4.9  | Allocation of jobs from the doors application                                                                                                                               |

| 4.10 | Resulting allocation of jobs                                                                                                                                                |

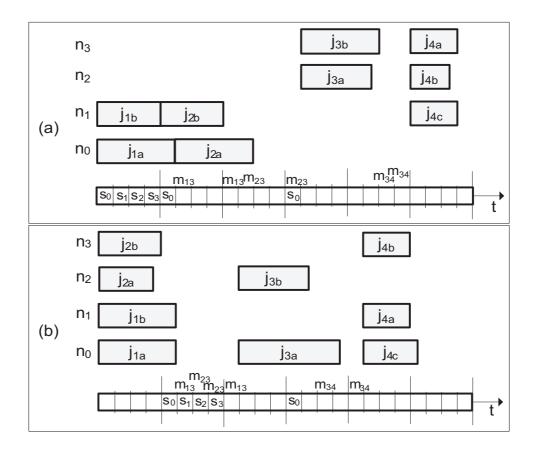

| 5.1  | Metrics of mapping configuration (a)                                                                                                                                        |

| 5.2  | Metrics of mapping configuration (b)                                                                                                                                        |

| 5.3  | Metrics of mapping configuration (c)                                                                                                                                        |

| 5.4  | Metrics of mapping configuration (d)                                                                                                                                        |

| 6.1  | Job properties                                                                                                                                                              |

| 6.2  | Speeding up the convergency                                                                                                                                                 |

| 6.3  | Performance profile $M_{PF}$ for 40 jobs                                                                                                                                    |

| 6.4  | Performance profile $M_{PF}$ for 60 jobs                                                                                                                                    |

| 6.5  | Performance profile $M_{PF}$ for 80 jobs                                                                                                                                    |

| 8.1  | Mapping configuration (a) and reliability                                                                                                                                   |

| 8.2  | Mapping configuration (b) and reliability                                                                                                                                   |

| 8.3  | Mapping configuration (c) and reliability                                                                                                                                   |

# List of Algorithms

| 1 | Generic methodology for system level design optimization | 67  |

|---|----------------------------------------------------------|-----|

| 2 | Network delay calculation for messages transmission      | 86  |

| 3 | Extra-functionality driven SW-HW mapping algorithm       | 94  |

| 4 | Satisfaction of constraints during the mapping           | 96  |

| 5 | General optimization process                             | 107 |

| 6 | The MVO algorithm                                        | 123 |

| 7 | Transformation operator $\Gamma$                         | 124 |

xviii

# Chapter 1

# Introduction

Embedded systems are becoming pervasive in our daily lives as well as in aspects where their proper functioning is crucial. Albeit hidden from the user, in reality we are surrounded by varied complexity embedded systems ranging from simple sensors, to wristwatch to cell phones, to the higher level *safety critical* systems used in *automotive, aerospace*, medical and control applications. Our growing use of embedded systems is driven by their sustained delivery of desired services despite the occurrence of perturbations. The perturbations range from electromechanical stresses, to system, software and communication level failures. For safety-critical systems, the need is to sustain operations in the presence of perturbations (*dependability*), this is often complemented by temporal requirements and the time duration by which a service is required (*real-time*) – also irrespective of the encountered perturbations.

The trend for the future is that more systems will contain computercontrolled/electronic components, i.e., will only increase the embedded controlled systems. Automotive original equipment manufacturer (OEM) such as DaimlerChrysler states that more than 90% of innovation (and hence value added) in a car will be in electronics and other OEM BMW indicates that more than 30% of the cost of manufacturing a car resides in the electronic components [1]. The worldwide value creation in automotive electrical and electronics systems, including SW, amounts to an estimated 127 billion EUR in 2002 and an expected 317 billion EUR in 2015 [2]. The trend is that use of electronics in modern car replacing critical mechanical and hydraulic components is increasing. The number and type of critical functions implemented by embedded electronic systems aboard a car and aeroplane is evolving as well. It is unforeseen that this trend will stop in near future. The design of such systems is becoming challenging and needs sound methods and techniques.

In general, *embedded systems* are defined as a class of special purpose computing system and are usually embedded (tightly or loosely) within a larger system; functionality is mostly fixed and dedicated; working very often in a reactive mode; responding frequently to external inputs; implemented by numerous concurrently working processes; infrequently reprogrammed; extensively sensitive concerning cost, power and performance criteria; have hard dependability [3] and correctness constraints, e.g., a brake-by-wire system aboard a car has to work bug-free and without interruption in any circumstances. The latter types are called as *dependable embedded systems*. These types of system may consist of micromechanical, microelectronic and increasingly use software components hence are heterogeneous containing hardware (HW) and software (SW) parts. Nearly all functions, for example, in vehicles and in aeroplane are controlled by *software components* (SW-Cs) running on microprocessors. The complexity of designing such systems is however growing at a very high pace through the integration of *mixed-criticality* applications (having both safety-critical and non-safety critical applications), through the use of multiprocessor cores, system-on-chip (SOC) architecture and through the high interactions between distributed applications. The constraints with respect to both functionality and *extra-functionality* are getting tighter as well. The extra-functional properties includes dependability/fault tolerance  $(FT)^1$ , reliability, timeliness, power, cost and time-to-market.

In order to obtain a *dependable* operation of embedded systems while maintaining *performance/timeliness* and *resource efficiency*, the design process of such complex systems is becoming an important issue and also difficult at the same time to meet varied requirements. Though the design approach presented in this thesis is applicable for various embedded systems like automotive, avionics, aerospace, control, seaborne, embedded mobile and wireless systems, throughout this writeup we focus on examples for automotive applications, where we devote to apply our developed methods and techniques, for both *safety-critical (SC) and non-SC* specially for *X-by-Wire* (XBW) [4; 5; 6] and other critical applications where 'X' stands for any SC applications such as Brake-, Steer-, Flight-by-Wire. The critical applications include powertrain, car engine control, heart pace-makers, nuclear power plant control and military radar systems. We provide a brief description of different classes of automotive applications as follows.

Automotive Applications: A new class of computer-driven automotive applications is emerging known as XBW systems which are categorized as composite SC and *hard real-time* (RT) embedded applications. These types

<sup>&</sup>lt;sup>1</sup>The terms dependability and FT will be used synonymously in the thesis.

of functionalities are used to control the movement of the car or assisting the driver. They are increasingly being implemented as SW replacing the mechanical and hydraulic systems in the car. The key benefits being enhanced processing capabilities, weight and cost. They often impose a high dependability requirements and tight RT constraints, e.g., the driver assistance system has to respond to the environment within a few milliseconds once it gets a request from the driver. The response has to be made correctly even in presence of any perturbations. These types of applications further include electronic stability programs, lane assistance, anti-lock brake systems, adaptive cruise control etc. Another type of applications implemented as SW-Cs is called as *body electronics*. These applications are less critical comparative to the ones defined earlier. The functionalities which control the simple electronic devices in the vehicle such as doors and window control, windshield wipers, lighting are categorized into this class. Usually they are classified in the category of safety relevant and also as non-SC applications. Recently many new and innovative functionalities are increasingly being deployed in the car for user comfort and communication. These are classified as infotainment and telematics applications. Examples of such applications include instrument cluster, in-car navigation systems, multimedia systems, car radio, hands-free phones, air conditioning system, car-to-car communication systems, etc. These are usually categorized as non-SC applications. During the design process care has to be taken such that there is no erroneous data or control flow from these types of applications or from applications of body electronics to the SC applications, i.e., the *fault/error propagation* from non-SC to SC application have to be prohibited by design.

Given the prime focus on designing SC embedded systems, we investigate some common idiosyncrasies of SC systems (as follows) which make the design of such systems challenging and look for new methodologies and tools.

- For embedded systems both the functional and extra-functional attributes are extensively defined by SW-C, i.e., by the so called embedded SW,

- These types of systems are composed of both SW-Cs and HW components (HW-Cs) which interact in order to perform the given task,

- Embedded system applications are distributed in nature and should be implemented over several microprocessors and HW architecture,

- The system often operates in SC contexts and has to provide services dependably, and

• Have to fulfill stringent *real-time* (RT) constraints, as well as constraints concerning timeliness, cost, weight, power and resource consumption.

The methodologies and techniques proposed in this thesis consider the conceptual and applied guidelines (a) to integrate such varied functionalities and characteristics of both SC and non-SC embedded applications, (b) to achieve dependability/FT, and (c) is followed by RT/timeliness, performance, power, resource and cost driven principles.

This chapter further provides a description of designing dependable embedded system at higher abstraction level, i.e., at *system level*. An introduction of different design techniques such as *federated and integrated* design approach, the need for *SW-HW co-design/integration* [7; 8; 9] and some evolving design challenges are described. The design at abstraction or system level implies the design process that hides the unnecessary implementation details. A short overview of system design for achieving and optimizing dependability is depicted. Subsequently the chapter describes the problem statement of the work and thesis research relevant questions. Finally the main contributions of the thesis are previewed including the publications and a short thesis outline is depicted.

### **1.1** System Level Design and Challenges