#### **Analysis and Detection of Cache-Based Exploits**

#### Vom Fachbereich Informatik der Technischen Universität Darmstadt genehmigte

#### Dissertation

zur Erlangung des akademischen Grades eines Doktor-Ingenieur (Dr.-Ing.) von

### Tsvetoslava Vateva-Gurova, M.Sc., geb. Vateva, aus Botevgrad, Bulgarien

Referenten: Prof. Dr. Guido Salvaneschi

Prof. Neeraj Suri, Ph.D. Prof. Dr. Stefan Katzenbeisser

Datum der Einreichung: 29. Oktober 2019 Datum der mündlichen Prüfung: 11. Dezember 2019

> Darmstadt 2019 D17

Vateva-Gurova, Tsvetoslava: Analysis and Detection of Cache-Based Exploits

Darmstadt, Technische Universität Darmstadt

Jahr der Veröffentlichung der Dissertation auf TUprints: 2020

URN: urn:nbn:de:tuda-tuprints-97706 Tag der mündlichen Prüfung: 11.12.2019

Nutzungsrechte gemäß UrhG.

# Analysis and Detection of Cache-Based Exploits

bу

Tsvetoslava Vateva-Gurova

| Ē | R  | K  | Τ. | Ä        | R  | IJ     | N   | G                |

|---|----|----|----|----------|----|--------|-----|------------------|

| · | Τ. | Τ. | u  | <i>1</i> | Τ. | $\sim$ | T . | $\mathbf{\circ}$ |

Hiermit versichere ich, die vorliegende Dissertation selbstständig und nur unter Verwendung der angegebenen Quellen und Hilfsmittel verfasst zu haben. Alle Stellen, die aus Quellen entnommen wurden, sind als solche kenntlich gemacht. Diese Arbeit hat in gleicher oder ähnlicher Form noch keiner Prüfungsbehörde vorgelegen.

| Darmstadt, 29. Oktober 2019 |                           |

|-----------------------------|---------------------------|

|                             |                           |

|                             | Tsvetoslava Vateva-Gurova |

#### **ABSTRACT**

Over the last decades the digitalization has become an integral part of daily life. Computer systems complexity has also grown at a rapid pace. New business models have emerged to optimize utilization and maintenance cost of these complex systems, but neglecting the introduction of new security threats. Cloud computing, for instance, has been established as an important part of the modern IT infrastructure ignoring the potential security risks entailed in its pervasive usage.

A popular threat in the Cloud and other complex systems that are reliant on the usage of shared resources stems from the exploitation of side channels. In the context of co-location of mutually untrusted users on the same hardware, the confidentiality of user data has to be guaranteed. However, the class of side-channel and covert-channel attacks has been demonstrated to circumvent the secure isolation between co-located users both in the Cloud and in a native environment by exploiting hardware side effects, e.g., through timing analyses of accesses to CPU caches. The threat related to these exploits has been known for decades, but its relevance has grown with the increasing popularity of Cloud services. In this context, the cache is leveraged as an illegal channel to convey information either from one adversary to another in a covert-channel attack or to leak information from a victim to an attacker in a side-channel attack. As cache usage does not require any privileges, addressing the threat resulting from such an exploit turns out to be a challenging task.

On this background, this thesis aims at enhancing systems security by considering the cache-based covert-channel and side-channel attacks. We develop a classification of existing attacks by exploring their feasibility depending on the execution environment context, and construct an information leakage model which includes the CPU scheduling effect on the core-private cache exploitability. To delve into the specifics of detecting cache exploits, we define a set of indicators of compromise and investigate their correlation with the success of a core-private cache exploit. To account for the effect of the hypervisor scheduling configuration on the exploitability of the core-private cache, we empirically assess the success of a covert-channel attack while varying hypervisor scheduling parameters. We employ software events and performance counters to develop a reliable detection mechanism tailored to find contemporary side-channel attacks.

The results presented in the thesis demonstrate that by utilizing deliberately selected indicators of compromise along with a comprehensive analysis, systems security can be significantly enhanced with respect to the cache exploitability.

#### KURZFASSUNG

In den letzten Jahrzehnten hat sich die Digitalisierung zu einem festen Bestandteil des täglichen Lebens entwickelt. Die Komplexität von Computersystemen hat ebenfalls zugenommen. Neue Geschäftsmodelle sind entstanden, um die Auslastung und die Wartungskosten zu optimieren, aber die damit verbundene Einführung neuer Sicherheitsbedrohungen wird häufig vernachlässigt. Cloud Computing hat sich als wichtiger Bestandteil der modernen IT-Infrastruktur etabliert trotz der potenziellen Sicherheitsrisiken, die mit seiner allgegenwärtigen Nutzung verbunden sind.

Eine verbreitete Bedrohung in der Cloud und anderen komplexen Systemen, die auf die Verwendung gemeinsam genutzter Ressourcen angewiesen sind, resultiert aus der Ausnutzung von Seitenkanälen. Diese Bedrohung ist seit Jahrzehnten bekannt, aber ihre Relevanz hat mit der zunehmenden Popularität von Cloud-Diensten zugenommen. In diesem Kontext kann der Cache als Seitenkanal genutzt werden, um die Datenübertragung zwischen Gegnern bei einem verdeckten Kanalangriff oder Datenexfiltration von einem Opfer bei einem Seitenkanalangriff zu ermöglichen. Da für die Verwendung des Caches keine Berechtigungen erforderlich sind, gestaltet sich die Bekämpfung der Bedrohung durch einen solchen Exploit als herausfordernd.

Vor diesem Hintergrund zielt diese Dissertation darauf ab, die Systemsicherheit zu verbessern, indem cache-basierte Seitenkanalangriffe berücksichtigt werden. Wir entwickeln eine Klassifizierung bestehender Angriffe, indem wir ihre Durchführbarkeit in Abhängigkeit vom Kontext der Ausführungsumgebung untersuchen und ein Modell erstellen, das den CPU-Schedulingeffekt auf die Ausnutzbarkeit des Core-Private-Cache einschließt. Um die Besonderheiten der Erkennung von Cache-Exploits zu untersuchen, definieren wir Gefährdungsindikatoren und untersuchen deren Korrelation mit dem Erfolg eines Core-Private-Cache-Angriff. Um die Auswirkung der Hypervisor-Scheduling-Konfiguration auf die Ausnutzbarkeit des Core-Private-Cache zu berücksichtigen, wird der Angriffserfolg unter Variation der Hypervisor-Scheduling-Parameter empirisch bewertet. Mithilfe von Software-Events und Performance Counters entwickeln wir einen zuverlässigen Erkennungsmechanismus, der auf das Auffinden aktueller Seitenkanalangriffe zugeschnitten ist.

Die in der Dissertation vorgestellten Ergebnisse zeigen, dass durch die Verwendung bewusst ausgewählter Gefährdungsindikatoren zusammen mit einer umfassenden Analyse die Systemsicherheit in Bezug auf die Cache-Ausnutzbarkeit erheblich verbessert werden kann.

#### ACKNOWLEDGMENTS

Pursuing the PhD was a long and intriguing journey. I was happy to spend my PhD years at the DEEDS group and to meet nice people along the way. I would like to thank my advisor Neeraj Suri for giving me this opportunity and the freedom to develop and explore my own research interests. I am grateful for your advises and your guidance throughout the whole PhD endeavour! I am also very grateful to Guido Salvaneschi for being my internal referent and to Stefan Katzenbeisser for accepting to be my external reviewer. I am thankful to Kirstin Peters, Christian Reuter and Thomas Schneider for being on my committee.

Pursuing the PhD requires an active research environment. Therefore, I would like to thank all my colleagues in the DEEDS group for being always open for discussions. I am thankful to my officemates Salman, Ruben and Jesus for the nice atmosphere in the office. I consider myself lucky in this regard. Although my Spanish did not improve tremendously, I learned a lot about Barcelona, Mallorca, football, the Pakistani culture and cuisine throughout the years! I am happy to have had discussions on formal modeling and diverse other technical and non-technical stuff with Habib and to get Nico's opinion on various topics related to our joint work and far beyond. I am glad for having supervised theses jointly with Olli and for our fruitful technical and non-technical discussions. I am thankful to Sabine for having a friendly ear for all my problems and being always helpful with the paperwork. I am also thankful to Ute for dealing with HotCRP and the website and for being ready to help. I am grateful for the feedback I have received throughout the years, for the nice lunch/coffee breaks and the insights I gained about karma, mustard and other important things in life. It's been a nice time! I am also happy that I met my former colleagues Heng, Thorsten, Ahmed, Hatem, Hamza, Daniel, Reza, Kubilay and Stefan. Each of them has contributed to the DEEDS spirit in their own way.

Last but foremost, I would like to thank to my family for being loving, supportive, patient and encouraging throughout all the years. Mostly, I am grateful for having my little daughter who taught me what is important in life, how to be more flexible and open-minded, and that everything is possible if you "just give it a try". Thanks Iliya, for your patience, love and advises. It has always been a great pleasure for me to have you by my side in stressful and less stressful times and I do know how lucky I am. Special thanks go to my parents Genka and Georgi for teaching me everything in life, being supportive and caring every time I needed it. I owe them a lot! Thanks also to my brother Nikolai for having an idea how to tackle whatever problem I had. I am grateful to my grandmothers and grandfathers for their love and positive energy and to my parents-in-law Anka and Pano for helping out any time it was needed. I feel extremely lucky for the family I got and appreciate their contribution to finish the PhD.

#### **PUBLICATIONS**

The following publications have, in parts verbatim, been included in this thesis.

- [VAT+14A] T. Vateva-Gurova, J. Luna, G. Pellegrino, and N. Suri. "Towards a Framework for Assessing the Feasibility of Side-channel Attacks in Virtualized Environments". In: *Proc. of the 11th International Conference on Security and Cryptography Volume 1: SECRYPT 2014, Vienna, Austria.* INSTICC. SciTePress, 2014, pp. 113–124. DOI: 10.5220/0005052101130124

- [VSM15] T. Vateva-Gurova, N. Suri, and A. Mendelson. "The Impact of Hypervisor Scheduling on Compromising Virtualized Environments". In: *Proc. of the 2015 IEEE International Conference on Computer and Information Technology; Ubiquitous Computing and Communications; Dependable, Autonomic and Secure Computing; Pervasive Intelligence and Computing, DASC 2015, Liverpool, United Kingdom, October 26-28. 2015, pp. 1910–1917. DOI: 10.1109/CIT/IUCC/DASC/PICOM.2015.283*

- [VAT+18] T. Vateva-Gurova, S. Manzoor, Y. Huang, and N. Suri. "InfoLeak: Scheduling-Based Information Leakage". In: *Proc. of the 23rd IEEE Pacific Rim International Symposium on Dependable Computing (PRDC) PRDC'18, Taipei, Taiwan, December 4-7, 2018.* 2018, pp. 44–53. DOI: 10.1109/PRDC.2018.00015

- [VG+19] Tsvetoslava Vateva-Gurova, Salman Manzoor, Ruben Trapero, and Neeraj Suri. "Protecting Cloud-Based CIs: Covert Channel Vulnerabilities at the Resource Level". In: *Proc. of Information and Operational Technology Security Systems, Heraklion, Crete, Greece, September* 13, 2018. Ed. by Apostolos P. Fournaris, Konstantinos Lampropoulos, and Eva Marín Tordera. Cham: Springer International Publishing, 2019, pp. 27–38

- [VGCS] T. Vateva-Gurova, N. Coppik, and N. Suri. "SpyAlarm: Be the Spy and Spy the Attacker". In: *Transactions on Dependable and Secure Computing* (). [under submission]

The following publications are related to different aspects covered in this thesis and have been published during my doctoral studies, but have not been included in the thesis.

[Hei+19] Markus Heinrich, Tsvetoslava Vateva-Gurova, Tolga Arul, Stefan Katzenbeisser, Neeraj Suri, Henk Birkholz, Andreas Fuchs, Christoph Krauß, Maria Zhdanova, Don Kuzhiyelil, Sergey Tverdyshev, and Christian Schlehuber. "Security Requirements Engineering in Safety-Critical Railway Signalling Networks". In: Security and Communication Networks 2019 (2019). DOI: 10.1155/2019/8348925

- [VS18] Tsvetoslava Vateva-Gurova and Neeraj Suri. "On the Detection of Side-Channel Attacks". In: *Proc. of the 23rd IEEE Pacific Rim International Symposium on Dependable Computing (PRDC) PRDC'18, Taipei, Taiwan, December 4-7, 2018.* 2018, pp. 185–186

- [BIR+18] Henk Birkholz, Christoph Krauß, Maria Zhdanova, Don Kuzhiyelil, Tolga Arul, Markus Heinrich, Stefan Katzenbeisser, Neeraj Suri, Tsvetoslava Vateva-Gurova, and Christian Schlehuber. "A Reference Architecture for Integrating Safety and Security Applications on Railway Command and Control Systems". In: International Workshop on MILS: Architecture and Assurance for Secure Systems, Luxembourg, 25.06.2018. Zenodo, 2018. DOI: 10.5281/zenodo.1314095

- [MAN+18] Salman Manzoor, Tsvetoslava Vateva-Gurova, Rubén Trapero, and Neeraj Suri. "Threat Modeling the Cloud: An Ontology Based Approach". In: *Proc. of Information and Operational Technology Security Systems, Heraklion, Crete, Greece, September* 13, 2018. 2018, pp. 61–72

- [SCH+17B] Christian Schlehuber, Markus Heinrich, Tsvetoslava Vateva-Gurova, Stefan Katzenbeisser, and Neeraj Suri. "Challenges and Approaches in Securing Safety-Relevant Railway Signalling". In: *Proc. of the 2017 IEEE European Symposium on Security and Privacy Workshops, EuroS&P Workshops* 2017, Paris, France, April 26-28, 2017. 2017, pp. 139–145. DOI: 10.1109/eurospw.2017.63

- [SCH+17A] Christian Schlehuber, Markus Heinrich, Tsvetoslava Vateva-Gurova, Stefan Katzenbeisser, and Neeraj Suri. "A Security Architecture for Railway Signalling". In: *Proc. of the 36th International Conference on Computer Safety, Reliability, and Security, SAFECOMP 2017, Trento, Italy, September 12*. IEEE, 2017, pp. 320–328

- [VAT+14B] Tsvetoslava Vateva-Gurova, Jesus Luna, Giancarlo Pellegrino, and Neeraj Suri. "On the Feasibility of Side-Channel Attacks in a Virtualized Environment". In: *E-Business and Telecommunications, ICETE 2014, Vienna, Austria, August 28-30, 2014, Revised Selected Papers*. Ed. by Mohammad S. Obaidat, Andreas Holzinger, and Joaquim Filipe. Springer International Publishing, 2014, pp. 319–339. DOI: 10.1007/978-3-319-25915-4\\_17

- [VES+14] Fatbardh Veseli, Tsvetoslava Vateva-Gurova, Ioannis Krontiris, Kai Rannenberg, and Neeraj Suri. "Towards a Framework for Benchmarking Privacy-ABC Technologies". In: Proc. of the 29th IFIP TC 11 International Conference on ICT Systems Security and Privacy Protection, SEC 2014, Marrakech, Morocco, June 2-4, 2014. 2014, pp. 197–204. DOI: 10.1007/978-3-642-55415-5\_16

- [Lun+13] Jesus Luna, Tsvetoslava Vateva-Gurova, Neeraj Suri, Massimiliano Rak, and Alessandra De Benedictis. "SecLA-Based Negotiation and Brokering of Cloud Resources". In: Cloud Computing and Services Science—Third International Conference, CLOSER 2013, Aachen, Germany, May 8-10, 2013, Revised Selected Papers. Springer International Publishing, 2013, pp. 1–18

- [GAR+13] Jesus Luna Garcia, Tsvetoslava Vateva-Gurova, Neeraj Suri, Massimiliano Rak, and Loredana Liccardo. "Negotiating and Brokering Cloud Resources based on Security Level Agreements". In: *Proc. of the 3rd International Conference on Cloud Computing and Services Science Volume 1: CloudSecGov, (CLOSER 2013).* SciTePress, 2013, pp. 533–541

- [GAR+12] Jesus Luna Garcia, Hamza Ghani, Tsvetoslava Vateva, and Neeraj Suri. "Quantitative Assessment of Cloud Security Level Agreements A Case Study". In: *Proc. of the International Conference on Security and Cryptography Volume 1: SECRYPT 2012, Rome, Italy.* 2012, pp. 64–73

- [Dem+18] Kubilay Demir, Hatem Ismail, Tsvetoslava Vateva-Gurova, and Neeraj Suri. "Securing the Cloud-Assisted Smart Grid". In: *International Journal of Critical Infrastructure Protection (IJCIP)* 23 (2018), pp. 100–111. DOI: 10.1016/j.ijcip.2018.08.004

#### CONTENTS

| 1  | INT  | RODUCTION 1                                                      |

|----|------|------------------------------------------------------------------|

|    | 1.1  | Security in a Complex IT World 2                                 |

|    | 1.2  | Exploiting Side Channels 4                                       |

|    | 1.3  | Research Questions and Contributions 6                           |

|    | 1.4  | Thesis Outline 9                                                 |

| I  | PRE  | LIMINARIES                                                       |

| 2  | SID  | E-CHANNEL AND COVERT-CHANNEL ATTACKS 13                          |

|    | 2.1  | Overview 13                                                      |

|    | 2.2  | The Cache as a Side Channel 14                                   |

|    | 2.3  | Strategies to Exploit the Cache as a Side Channel 15             |

|    |      | 2.3.1 Side-channel Attack Strategies which do not Require Shared |

|    |      | Memory 15                                                        |

|    |      | 2.3.2 Shared Memory and Side-Channel Attack Approaches 17        |

|    | 2.4  | System and Attacker Models 18                                    |

| тт | 0.11 |                                                                  |

| II |      | THE CLASSIFICATION, FEASIBILITY AND MODELING OF SIDE-            |

| _  |      | ANNEL ATTACKS                                                    |

| 3  |      | VARDS THE SYSTEMATIC REASONING ABOUT SIDE-CHANNEL AT-            |

|    | TAC  |                                                                  |

|    | -    | Classification and Feasibility Endeavours 23                     |

|    | 3.2  | Side-channel Attacks Classification Approach 25                  |

|    |      | 3.2.1 Approach 25                                                |

|    |      | 3.2.2 Offline analysis 27                                        |

|    |      | 3.2.3 Effect 27                                                  |

|    |      | 3.2.4 Limitations 28                                             |

|    | 3.3  | Feasibility of SCAs 32                                           |

|    |      | 3.3.1 Feasibility factors 33                                     |

|    | 3.4  | Related work 35                                                  |

|    |      | 3.4.1 Classification of Side-Channel Exploits 35                 |

|    |      | 3.4.2 Feasibility Assessment of Cache-Based Side-Channel At-     |

|    |      | tacks. 37                                                        |

|    | 3.5  | Conclusion 37                                                    |

| 4  | MOI  | DELING OF CACHE-BASED EXPLOITS 39                                |

|    | 4.1  | On the Modeling of Cache-Based Exploits 39                       |

|    | 4.2  | Modeling the Side-Channel with InfoLeak 40                       |

|    |      | 4.2.1 Channel Users 40                                           |

|    |      | 4.2.2 Channel States 41                                          |

|    |      | 4.2.3 Channel Interactions 41                                    |

|    | 4.3  | Modeling the Scheduling Effect 43                                |

|    |      | 4.3.1 Discussion and Possible Extensions 44                      |

|    |      | 4.3.2 On the Application of InfoLeak 45                          |

|     | 4.4 | Related Work 47                                                               |

|-----|-----|-------------------------------------------------------------------------------|

|     |     | 4.4.1 Information Leakage Modeling 47                                         |

|     | 4.5 | Conclusion 48                                                                 |

| III | EMF | PIRICAL ANALYSIS OF THE EFFECT OF THE EXECUTION ENVIRON-                      |

|     | MEN | NT ON THE SCAS                                                                |

| 5   | cov | ERT-CHANNEL ATTACKS AND THEIR TRACES 51                                       |

|     | 5.1 | On the Indicators of Cache-Based Exploits 51                                  |

|     | 5.2 | CPU Scheduling and Attack Traces 52                                           |

|     |     | 5.2.1 Scheduling-Related Considerations 52                                    |

|     |     | 5.2.2 Attack Indicators Selection 53                                          |

|     | 5.3 | Experimental Setup and Results 54                                             |

|     |     | 5.3.1 Setup 54                                                                |

|     |     | 5.3.2 Implementation Details 54                                               |

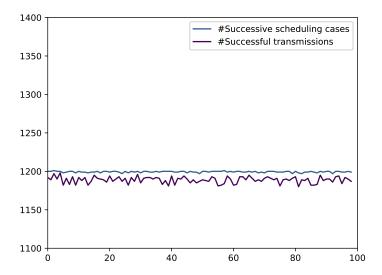

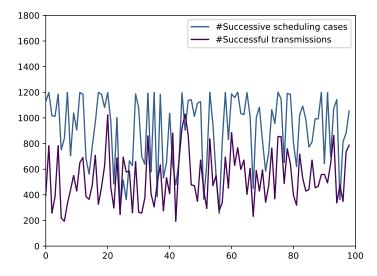

|     |     | 5.3.3 Successive Scheduling Experiments and Results 56                        |

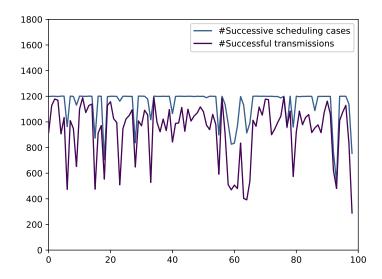

|     |     | 5.3.4 Busy Waiting Experiments and Results 59                                 |

|     | 5.4 | Related Work 61                                                               |

|     |     | 5.4.1 Synchronization and the Exploits of the Cache as a Side                 |

|     |     | Channel 61                                                                    |

|     | 5.5 | Attack Indicators – Summary and Discussion 62                                 |

| 6   | _   | EFFECT OF THE HYPERVISOR SCHEDULING CONFIGURATION 63                          |

|     | 6.1 | Overview 63                                                                   |

|     |     | System Model 64                                                               |

|     | 6.3 | Hypervisor Scheduler 65 6.3.1 Credit Scheduler 66                             |

|     |     |                                                                               |

|     | 6.4 | 6.3.2 Hypervisor Scheduling Parameters 66 Hypervisor Scheduling Evaluation 68 |

|     | 6.4 | 6.4.1 Experimental Setup 68                                                   |

|     |     | 6.4.2 Implementation Details 68                                               |

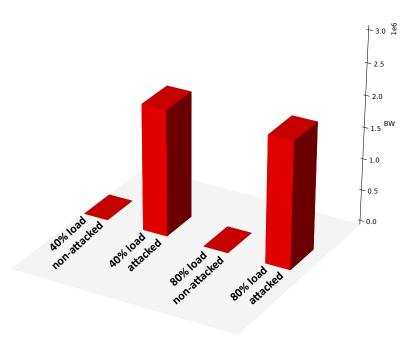

|     | 6.5 | The Role of Scheduling Parameters – Results 69                                |

|     | 6.6 | Related Work 73                                                               |

|     |     | 6.6.1 The Scheduling Effect 73                                                |

|     | 6.7 | Conclusion and Summary 74                                                     |

|     | ,   |                                                                               |

| IV  | ON  | THE DETECTION OF SIDE-CHANNEL ATTACKS                                         |

| 7   | SPY | ALARM – A RELIABLE CACHE-BASED EXPLOITS DETECTOR 79                           |

|     | 7.1 | The Need to Spy the Spy 79                                                    |

|     | 7.2 | System and Attacker Models 80                                                 |

|     | 7.3 | Approach 81                                                                   |

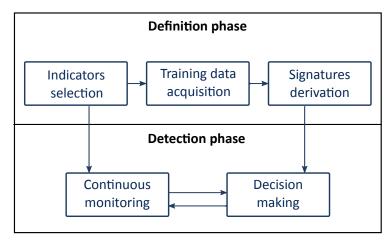

|     |     | 7.3.1 Definition Phase 81                                                     |

|     |     | 7.3.2 Detection Phase 83                                                      |

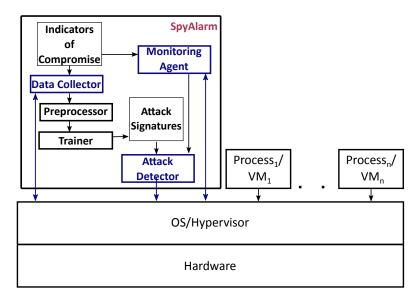

|     | 7.4 | Architectural Overview and Implementation 83                                  |

|     |     | 7.4.1 Architecture 84                                                         |

|     |     | 7.4.2 SpyAlarm Implementation Details and Parameters Consider-                |

|     |     | ation 85                                                                      |

|     | 7·5 | SpyAlarm Evaluation 87                                                        |

|     |     | 7.5.1 Experimental Setup 87                                                   |

```

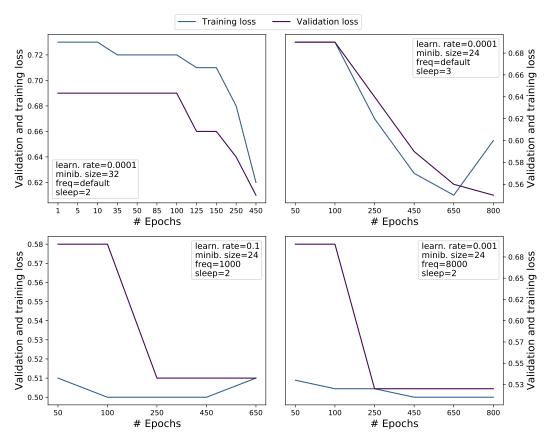

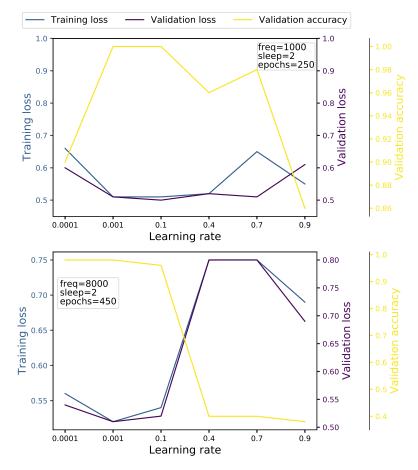

7.6 Detection Results

93

7.6.1

SpyAlarm Detection Accuracy

93

7.7 Challenges and Discussion

Limited Resources and Non-determinism

7.7.1

96

7.7.2

Choice of Events

97

7.7.3

Supervised Learning Algorithm and Training Data

7.8 Related Work

7.8.1

Covert-Channel and Side-Channel Attacks and their Mitiga-

tion

7.8.2 Detection and Attestation Approaches

103

7.9 Conclusion

105

V conclusion

8 SUMMARY AND CONCLUSION

```

#### INTRODUCTION

Security is always excessive until it is not enough

Robbie Sinclair

Computer systems have become a significant part of our lives while evolving at a rapid pace. Over the last decades they have continuously grown in complexity both in terms of hardware and software. For years hardware has undergone a considerable improvement in speed and space utilization complying with Moore's law [Moooo], which has predicted a doubling of the number of transistors every second year. Although Moore's law does not necessarily characterize the current hardware development trend anymore [Hea18], hardware is still becoming more complex to compensate, e.g., through massively parallel architectures. Due to this rapid development, the existing hardware has been able to easily solve general purpose tasks for decades now which enables the ubiquitous usage of computing power.

As a result, almost every area of nowadays life is dependent on digitalisation or computing. Business, administration, medical care and research are just a few examples of domains that rely on modern computing. Consequently, more and more personal data such as medical records or browsing history is collected in a digital form for various purposes with or without user consent. As an example, advertisement services have become reliant on targeting their audience by analyzing data focused on customer interests. The increase in data gathering practices has become so ubiquitous that legislation was introduced to rein the collection of personal data. The European Union adopted the General Data Protection Regulation (GDPR) [Gdp] in 2016 to regulate the gathering of personal data related to individuals in the European Union. A similar proposal, known as the California Consumer Privacy Act [Ccp], was enacted on the 28th of July, 2018 in California to impose new data protection requirements on companies while granting new rights to the consumers with respect to the collection of their personal data.

The software that enables this rapid development and the processing of huge amounts of data also grows in size and complexity. Spinellis et al. show in their work [SA19] that the codebase of the modern operating systems has drastically grown. For instance, the number of lines of kernel code for Research PDP7 has evolved from 2489 in 1970 to about 8518968 lines of kernel code in FreeBSD 11.0.0 in 2016 [SA19]. Similarly, the number of lines of code of OpenSSL [Ope] has increased from less than 200000 in 2000 to more than 500000 in 2019. In addition,

the interconnectivity of various types of devices (cars, mobile phones, etc.) has also increased. Concepts such as Internet of Things and Artificial Intelligence dealing with huge amounts of data, and creating sophisticated prediction models are now well-established. The systems are getting more complex in every thinkable dimension.

The increased usage of and reliance on the Internet and digitalization has emphasized the need for solutions that facilitate the optimized utilization of resources, and concepts focused on the shared usage of resources have emerged. Cloud computing services, for instance, have gained much popularity for their cost efficiency, high availability and on-demand up and down scaling. This is why Cloud computing has become prevalent for numerous applications. According to Gartner, Inc., the Cloud services industry will grow exponentially through 2022 at nearly three times the growth of overall IT services [Gar19]. Moreover, the Healthcare Information and Management Systems Society (HIMMS) Analytics conducted a study in 2014 [HIM14] which confirmed the increasingly wide-spread adoption of Cloud services in critical sectors such as healthcare which deal with highly sensitive private information. Being widely used even in critical sectors, Cloud computing providers need to guarantee secure environments for their customers. Relying intrinsically on shared resources, the Cloud customers have to be securely isolated from each other without the possibility to leak information from the co-located customers.

Along with the benefits and advantages the technological innovations brought along, the risk of loosing control over personal data and the unpredictability of software behavior, especially in the context of increasing system complexity and resource sharing, has risen. The growth in software complexity leads to potential increases in the attack surface and can open up new vulnerabilities. The National Vulnerability Database (NVD) [Nis] maintained by the US National Institute for Standards and Technology (NIST) contains more than 16000 vulnerabilities (i.e., flaws in software which can be exploited by an attacker) reported in 2018 compared to less than 2000 vulnerabilities reported in 2003 and approximately 2500 vulnerabilities reported in 2004 [Nis]. The increased number of vulnerabilities demonstrates the relevance of security nowadays in the complex IT world and indicates the need for rigorous methods to address the existing security issues.

#### 1.1 SECURITY IN A COMPLEX IT WORLD

In the context of wide-spread data collection and sharing of resources across security boundaries, the importance of security and in particular the confidentiality of data only increases. Data confidentiality "deals with protecting against the disclosure of information by ensuring that the data is limited to those authorized or by representing the data in such a way that its semantics remain accessible only to those who possess some critical information (e.g., a key for decrypting the enciphered data)" according to the definition provided by NIST [Infa]. The data confidentiality property guarantees that the data is not made available or disclosed to unauthorized entities, individuals or processes, and the confidential information

has to be kept securely disallowing unauthorized access. It is usually achieved by the means of encryption.

Data confidentiality is vital to Cloud computing systems due the usage of shared resources across security boundaries. In fact, the requirement of secure isolation between co-located customers dates back decades. Commonly, the underlying technology in Cloud computing is virtualization which enables the co-location of users across security domains encapsulated in virtual machines. Among the early requirements on virtualization, as defined by Popek [PG74], is the isolation of a virtual machine. This property includes the requirement that the co-located virtual machines cannot compromise the confidentiality of each other. Today, with the increased complexity of computer systems and software, the relevance of this requirement has increased.

Although security is a necessary property for a variety of application scenarios, addressing security requirements can be challenging. For already well-established legacy systems enhancing security entails an increase in terms of cost, and might introduce performance overhead or usability issues. Depending on the system, fixing security issues or adapting to changing threats may even require renewing the standardization of the system, and performing a whole standardization procedure from the beginning. This is, for example, often the case in critical infrastructures such as railway systems. Such issues make system administrators sometimes reluctant to incorporate proper security solutions into their systems unless it is urgently necessary. Furthermore, the adoption of new security solutions and replacing of old ones is often cumbersome and slow.

This is a wide-spread issue in cryptographic software, where legacy ciphers are frequently supported long after their deprecation, which can lead to exploiting security flaws. In 2016 the Sweet32 vulnerability (CVE-2016-2183 and CVE-2016-6329) has been reported to exploit the 3DES encryption algorithm [BL16]. The 3DES algorithm has been considered a legacy cipher for quite some time, and the reported attack emphasizes the need to retire weaker algorithms such as 3DES. Despite this fact, according to the authors of the reported vulnerability, 3DES had been used for about 1-2% of all HTTPS connections between mainstream browsers and web servers. About a year after the Sweet32 vulnerability report, in July 2017, NIST has withdrawn the approval for using 3DES in protocols such as TLS and IPSec. NIST has declared the algorithm as officially retired in a draft guidance published in July, 2018 [BR19]. Similarly, Microsoft announced in April 2019 that 3DES algorithm will be retired beginning of July 2019, about three years after the Sweet32 vulnerability report [Ari19]. This example confirms that the adoption of contemporary security solutions is commonly slow and cumbersome, and compromised solutions might be still in use.

The human factor is often an additional reason for the slow changes related to systems security. User frustration and lack of knowledge often pose a challenge when incorporating security measures to existing systems. Recently, Stark et al. [Sta+19] reported on their experience on deploying a security solution that tackles the danger of improper certificate issuance and can provide desirable security benefits, but its full deployment would represent a huge change to the HTTPS ecosystem. They also studied user behavior in the cases of breakage and

came to the conclusion that user behavior is unsafe. Another experiment based on a cyber-physical systems game described in [Fre+17] demonstrated that even the security experts involved in the experiment tended to neglect intelligence gathering. Being that confident in their expertise, the security experts often skipped threat assessment which had implications on their performance within the study. Facing such challenges contributes to the cumbersome and slow addressing of security requirements and issues, and despite the pervasive deployment of cryptographic solutions to enhance system security, confidential data often remains insecure.

While addressing security issues in software and protocols is cumbersome and slow, current architectures are intrinsically insecure, and the vulnerabilities resulting from hardware properties are even harder to tackle. The employed hardware optimizations have resulted in a tremendous performance upgrade over the years, but are often related to security implications confirmed by the wide range of covert-channel attacks and side-channel attacks. These classes of attacks with their different manifestations are often a result of the hardware design exhibiting side effects. The existence of such powerful attacks that can compromise system's confidentiality is theoretically known for more than two decades. However, the system's performance is often at odds with the system's security and, in such cases, when security comes at a price, it is often being neglected.

#### 1.2 EXPLOITING SIDE CHANNELS

A side-channel attack is defined as an attack that is enabled by information leakage stemming from a physical ecosystem [Infb]. These attacks are based on characteristics resulting from the shared usage of or access to resources such as timing, power consumption, acoustic and electromagnetic emissions, etc. Side-channel attacks pose a threat to confidentiality and are hard to detect or prevent. In a side-channel scenario, an adversary observes victim's usage of a shared component and can extract victim's sensitive data based on analysis of the collected observations.

A similar exploit represents the covert-channel attack. A covert channel, as defined in [Infc], is a channel which is not intended or authorized for communication, but enables the information transfer between two cooperating entities. This happens in a way that violates the system's security policy but the involved entities do not exceed their access authorizations. Similar to the side-channel attack, a covert-channel attack exploits hardware side effects such as timing information.

Nowadays, top security conferences are concerned with the investigation of the covert-channel and side-channel exploits, and devote a significant part of their programs to the threat related to the misuse of side effects [Ccs; Spp]. At the same time, major providers such as VMWare or Amazon provide solutions that exclude different side-channel exploit possibilities [Ama14; VMwb]. This trend emphasizes the relevance of the covert-channel and side-channel exploits. Side-channel and covert-channel attacks abusing the side effects of the cache are in the focus of the thesis and are discussed in more detail in Part I. Within the thesis, the term "side channel" is used to denote the leakage channel in the context of both side-channel attacks and covert-channel attacks.

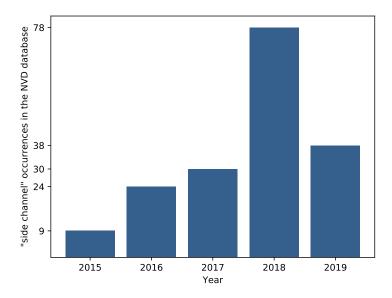

Figure 1: Occurrences of Side-Channel Vulnerabilities in the NIST National Vulnerability Database [Nis].

Currently, the research focuses on (i) proposals of new ways to exploit varied features of the computer architectures which emanate side effects; (ii) novel measures to combat the proposed exploits; and (iii) ways to detect them. In the course of the last decade security gaps stemming from the abuse of side effects have been closed, but new gaps have been opened up. This trend shows that the side-channel problem has not been solved. The number of the officially published vulnerabilities in NVD [Nis] emanating from side channels and exhibiting from low to critical severity has risen over the last years, as shown in Figure 1. On this background, what is currently clear is that side-channel and covert-channel attacks are hard to tackle despite representing a serious threat to the complex computer world and despite the extensive research being conducted on the topic.

The side-channel threat is basically related to all the thinkable components of a device, ranging from a power adapter (cf., [MDS99]), monitor (cf., [Gen+19]), keyboard (cf., [GST14; SWT01]) to cache memory (e.g., [Per05; Yan+19]). Commonly, each risky component is considered separately, and often mitigation strategies tailored to combat specific attacks are developed and proposed. Then, new manifestations of, theoretically, the same attack are discovered which might focus on a different component. A recent example for this development is the work conducted by Yan et al. [Yan+19] which demonstrates the feasibility of side-channel attacks on the sliced non-inclusive last-level cache of Intel Skylake-X architecture which has been considered more secure against last-level cache-based exploits. This work reconfirms that side-channel attacks are not an elusive threat, and research on them is expected to continue at least at the same pace.

#### 1.3 RESEARCH QUESTIONS AND CONTRIBUTIONS

This thesis investigates the research questions stated below, and extends the field of research by making the contributions summarized under the respective research questions. The overall goal of this work and the common line in the research questions is the investigation of cache-based side-channel and covert-channel attacks, referred to as cache-based exploits, and their interplay with the execution environment. In the focus of the thesis are both the effect of the execution environment on the cache-based exploits, and the effect of these exploits on the execution environment, i.e., their possible traces. The thesis aims at enhancing the security of systems relying on shared resources by providing a side-channel attacks detection mechanism, and assessing their interaction with the execution environment. The individual research questions are discussed below.

Research Question 1 (RQ1) Can we classify and model side-channel exploits considering the impact of the execution environment on their feasibility?

Side-channel and covert-channel exploits have been a known threat for decades, and they continue to grow in popularity. Such exploits are especially relevant in Cloud scenarios where resource sharing across security boundaries is commonplace. It has been demonstrated that side-channel attacks can enable data exfiltration and allow attackers to extract confidential information, such as secret keys. Currently, there is no universal solution for coping with this threat, and this is aggravated by the fact that the diversity of side-channel attacks continues to grow. Still, not every reported side-channel attack is feasible under any condition. While side-channel exploitation in the real-world commonly depends on particular properties of the execution environment (e.g., scheduling), the explicit consideration of these properties is often neglected.

Therefore, it will be beneficial to classify the side-channel attacks while considering the factors and properties which characterize the assumed execution environment. Formal modeling of the side channels that include the execution environment's impact is necessary to understand the risk of a particular cache-based exploit in a specific system.

Contribution 1 (C1): A classification approach of side-channel exploits and a side-channel attack model that take execution environment factors into account

A panoply of resources can be exploited to leak information as a side channel. To better understand the risk associated with the exploitation of these resources, this thesis proposes a classification approach for the side-channel exploits. Depending on the context, these attacks can be fairly difficult to conduct in a real-world setting, or their execution can be facilitated, e.g., due to the scheduling configuration.

We provide a classification framework that aims to describe the side-channel attacks based on their execution context to aid the analysis and assessment of their specific characteristics resulting in possible detection or mitigation mechanisms. Based on the proposed classification framework, we focus on the feasibility of

side-channel attacks that exploit cache memory in a virtualized environment. The goal of this contribution is to facilitate the systematic reasoning in regard to the side-channel threat along the feasibility assessment and modeling with respect to exploits of cache side effects.

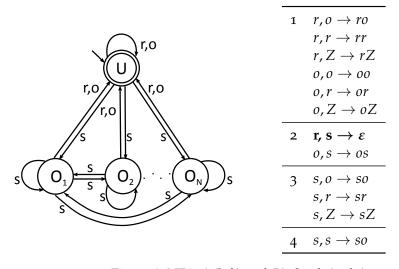

Additionally, we introduce InfoLeak, an information leakage model that ascertains the essential role of the CPU scheduler for exploiting core-private caches as side channels. InfoLeak illustrates the impact of the CPU scheduling on the availability of the core-private cache to the adversary that exploits it as a side channel. Our model enables security experts to consider the associated threat stemming from the core-private cache exploits by analyzing the available scheduling information. We provide an example on InfoLeak usage to demonstrate its applicability for studying the scheduling related logs for possible information leakage. This first contribution of the thesis is presented in Part II and is based, partly verbatim, on material from [Vat+14a; Vat+14b; Vat+18].

Research Question 2 (RQ2): What is the relationship between execution environment properties and the success and feasibility of side-channel attacks?

As side-channel mitigation approaches against particular attacks have been proposed to reduce the information leakage by tweaking the execution environment, it would be beneficial to analyze which of the execution environment properties affect the feasibility of the side-channel exploits and to what extent. Although various components can be exploited to leak information, certain classes of attacks might exhibit the same characteristics. For example, most of the cache-based approaches rely on timing of memory accesses to derive confidential information. Additionally, in a variety of scenarios the adversary needs frequent access to the side channel to be able to obtain sufficient observations of good quality or high granularity. This is related to the synchronization between the attacker and the victim which is of crucial importance for a number of cache-based adversary scenarios.

To this end, employing indicators or metrics which characterize the execution environment in regard to the synchronization possibility between a potential adversary and a victim in the context of core-private cache-based attacks is an enabler for finding potential side-channel attack traces. It is also important to investigate how the scheduling configuration affects the synchronization and consequently the chance of success of a cache-based side-channel exploit.

Contribution 2 (C2): Empirical evaluation of the impact of scheduling on side-channel attacks and their potential traces

The feasibility of side-channel attacks strongly depends on the context of the execution environment including the availability of the exploited shared resource. However, the characteristics of the specific attack must also be considered in order to evaluate the exploitability of an execution environment.

We characterize the context of the execution environment by proposing three attack indicators or metrics and study their correlation with the success of a coreprivate cache-based attack post-mortem. The proposed metrics are related to the means an attacker often employs to gain sufficient observations of the side channel when exploiting the core-private cache. We also discuss the applicability of the proposed feasibility metrics in a case study.

Additionally, we analyze the impact of the hypervisor scheduling configuration on the exploitability of the core-private cache as a side channel in a virtualized environment. For this purpose, we identify the relevant hypervisor scheduling parameters and conduct an empirical study on the success of the attack depending on different configurations. This contribution of the thesis is presented in Part III and is based, partly verbatim, on material from [VG+19; VSM15; Vat+18].

Research Question 3 (RQ3): Can side-channel attacks be reliably detected?

Although attacks at the architectural level represent a serious threat to data confidentiality, and enable information exfiltration, they are usually neglected by techniques, such as intrusion detection, which commonly focus on high-level network or middleware threats. This is magnified by the fact that side channels usually fall outside the scope of any security policies or access rules. Cache-based side channels, for instance, are accessed without any special privileges.

In this context and given the relevance of cache-based side-channel attacks, investigating the possibilities of detecting side-channel exploits is important for the security community. This is reinforced by the lack of a universal remedy against the side-channel threat posed by the current vulnerable cache design.

Contribution 3 (C3): A reliable side-channel attack detection approach using performance counters and software events

Existing approaches to mitigate or prevent covert-channel and side-channel attacks are usually limited by performance overhead, or they are too costly. Thus, incidents and anomalies related to the usage of the cache as a covert communication channel need to be detected, ideally without requiring new hardware. Traditional intrusion detection systems are not suitable for this purpose due to the lack of policies or access rights for the usage of the side channel.

In this contribution, we focus particularly on the detection of side-channel and covert-channel attacks that abuse the cache. We propose a side-channel detection approach, called SpyAlarm, based on the usage of metrics that indicate the feasibility of such attacks given the execution environment properties and their traces. SpyAlarm leverages a combination of performance counters and software events to reliably detect cache-based exploits while exhibiting a low false positive rate. In this contribution, we also present the SpyAlarm architecture and demonstrate its utility with a prototype implementation. To evaluate our approach, we apply it in several case studies including two state-of-the-art cache-based attacks previously unseen by the detector. Our results demonstrate the utility of SpyAlarm as a reliable side-channel detector, which enables triggering further actions to contain the damage caused by an attacker. This last contribution of the thesis is presented in Part IV and is based, partly verbatim, on material from [VGCS].

#### 1.4 THESIS OUTLINE

The rest of the thesis is structured as follows: In Part I various side-channel exploit strategies are covered, and the system model on which this thesis relies is presented. In Part II, the first research question is discussed, and a side-channel attacks classification approach which focuses on the feasibility factors affecting the attack's success is presented. Part II also includes a leakage model that advocates the scheduling effect on the success of the attack. In Part III the thesis continues with the analysis of the impact of different scheduling parameters, and the footprint cache-based exploits leave on a set of measurable system events. The third research question, which tackles the detectability of cache-based covert-channel and side-channel attacks, is investigated in Part IV. Finally, Part V concludes the thesis with a summary of the contributions and key insights.

## Part I PRELIMINARIES

#### SIDE-CHANNEL AND COVERT-CHANNEL ATTACKS

#### 2.1 OVERVIEW

Lampson is among the first researchers to mention the term "covert channel" as an illegal transmission channel which has not been designed to transmit information [Lam73]. Covert channels are leveraged in covert-channel attacks that involve two or more processes which collaborate to communicate with each other. The communication takes place through a shared resource which can be manipulated and measured by all the involved processes. There are various application scenarios for these attacks. For example, they can be used for secret transmission of information. The hardly detectable existence of such covert communication makes these transmission channels quite elusive. Among others, there are proposals to leverage covert channels to bypass censorship [Fea+02] or to use them to transmit authentication data [dAJ05].

Side-channel attacks can be seen as a variant of the covert-channel problem. Contrary to a covert-channel attack, where the cooperation between processes is the main goal of the collaborating attackers, a side-channel attack is a purely adversarial problem. A side-channel attacker spies on the actions of a co-located victim process and tries to extract secret data from the collected observations. This is possible due to the nature of the commonly used hardware exhibiting measurable side effects which often depend on the data or instructions being processed in various computations.

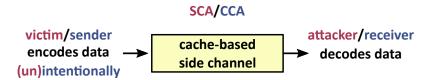

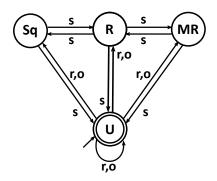

Figure 2: Covert-Channel Attack and Side-Channel Attack - Interaction with the Channel.

As can be seen in Figure 2, common for the covert-channel and the side-channel attacks is the usage of a shared resource as a transmission medium. If we consider the notion introduced by Shannon in his theory on communication [Shao1], the victim plays the role of the information source in a side-channel attack, whereas this role is taken over by the sender in a covert-channel attack. The channel is in both cases the shared medium. The transmitter that encode the message into the channel is the process of the victim that leaves traces in a side-channel attack, or it is the sender process in a covert-channel attack. The message itself can be a secret key in a side-channel attack and some other meaningful information in a

covert-channel attack which might be encoded, e.g., as a cache footprint. In such a case, the cache footprint represents the signal. The attacker process, spying on the victim, or the receiver process, trying to decode the message, is the receiver of the communication.

A major distinction between a side-channel attack and a covert-channel attacker lies in the fact that the side-channel attacker has to conduct a thorough analysis of the gathered data which is more complicated than the analysis a covert-channel attacker has to conduct. The covert-channel adversary decrypts a message that has been sent to him/her over the shared resource intentionally by a collaborating attacker. Commonly, the covert-channel receivers are reliant on a predefined shared usage pattern of the shared resource with the sender.

To avoid confusion, the shared resource which can be exploited as a covert or side channel is in both cases referred to as a side channel from now on in the thesis. It has been demonstrated already that the cache can be exploited as a side channel also in complex systems such as the Cloud. As it is easily accessible without the need of any special privileges in various execution environments, the cache represents a powerful and convenient side channel.

#### 2.2 THE CACHE AS A SIDE CHANNEL

As already discussed, the processors used to become faster complying with Moore's law. However, the memory speed, though increasing, did not develop at the same pace. To close the performance gap between the processors and the memory, caches were introduced as an important optimization, deployed universally. Depending on the applied caching algorithm, recently or frequently used data or instructions are fetched from the main memory into the cache and can be accessed much faster if they are needed repeatedly. If the requested data is already in the cache, a cache hit takes place and the latency for accessing the data is low. The smaller the cache containing the data, the faster the access to the requested data is. If the data is not in the cache, a cache miss takes place and the data has to be fetched into the cache from the main memory. This is, logically, associated with a longer latency and accessing the data takes more time than in the case of a cache hit.

Most computer architectures organize the caches in a hierarchical manner. Typically, there are two or three cache levels. The core-private caches, i.e., level 1 caches (L1), are faster and smaller and are located closer to the CPU. L1 cache is private per core and is usually divided into L1 instruction cache which stores instructions and L1 data cache which stores data. The last-level cache (LLC) is commonly shared among all cores and is unified, i.e., it stores both instructions and data.

Within the cache, the data is stored into units called cache lines or cache blocks. They are organized into cache sets. Each cache set consists of w cache lines, where w is referred to as cache associativity. A part of the memory address, often called set index, usually determines the cache set a cache line is mapped to.

In addition to that, the LLC of most modern Intel processors is further divided into slices mainly to reduce congestion [Int]. A hash function is applied to determine the slice of a cache line, but this hash function has not been published officially by the time of writing this thesis. Yarom et al. developed a technique to

reverse-engineer the hash function for certain architectures and published their work in [Yar+15].

Furthermore, modern LLCs are often inclusive which means that they contain a strict superset of the contents of the data contained in the lower cache levels [Int].

The access times to the different cache levels and the memory are measurable and, practically, almost each process running on a system can collect observations on the access times to the cache. This variance in the access times to the caches depending on whether a cache hit or a cache miss takes place, is a hardware side effect which can be abused by an attacker and enables powerful side-channel and covert-channel attacks.

#### 2.3 STRATEGIES TO EXPLOIT THE CACHE AS A SIDE CHANNEL

The cache was introduced to close the performance gap between the processors and the memory by overcoming the high latency of the memory. These universally deployed optimizations can be exploited by an attacker to leak confidential information from a process using the same cache.

On this background, there exist different strategies to abuse the cache to leak information. The existing attack strategies can be basically divided into attacks relying on the usage of shared memory between the attacker and the victim, and approaches that do not require shared memory. Among the well-known side-channel attack strategies are Evict+Time and Prime+Probe, described, e.g., [Liu+15; OSTo6; Pero5], Flush+Reload demonstrated in [YF14], and Flush+Flush proposed in [Gru+16].

#### 2.3.1 Side-channel Attack Strategies which do not Require Shared Memory

Unlike other strategies, Evict+Time and Prime+Probe do not rely on shared memory. They are characterized by a lower bandwidth compared to the approaches leveraging shared memory, but are still considered more powerful, as they do not depend on restrictions such as shared memory and therefore, can be applied on more systems.

#### 2.3.1.1 *Evict+Time*.

Among the first strategies to exploit the cache as a side channel is Evict+Time, proposed by Osvik et al. [OSTo6]. Evict+Time assumes the ability to trigger an encryption of known plaintext **p** on victim's side and to be able to determine when the encryption starts and when the encryption process ends. Before the encryption, the adversary manipulates the cache state. Then, the attacker lets the victim encrypt the plaintext. After the encryption, the attacker accesses selectively chosen addresses to evict specific cache lines. Then, the adversary triggers another encryption of the same plaintext **p** on the victim's side and measures the time the encryption takes. Longer encryption times indicate that the selectively evicted cache lines had to be fetched from the main memory suggesting that the victim has accessed these specific cache lines. The collected timing data is analyzed to

extract secret data. Bernstein applied a similar approach to extract an AES key, as described in [Bero5]. The main steps of the approach are summarized below.

- 1. Trigger encryption of plaintext **p**.

- 2. Evict specific cache lines by accessing appropriate addresses.

- 3. Trigger another encryption of plaintext **p** and measure the time the encryption takes.

Evict+Time is a time-driven side-channel attack which is reliant on measuring the overall execution time of victim's code. Evict+Time attackers typically observe the aggregated number of cache hits and cache misses which might result in coarse observation granularity. Despite that this approach still represents a security threat and was recently applied by Gras et al to demonstrate the insecurity of the Address space layout randomisation (ASLR) in [Gra+17].

#### 2.3.1.2 Prime and Probe.

Another approach exploiting the cache as a side channel, called Prime+Probe, was described by both Osvik et al. in [OSTo6] and by Percival in [Pero5]. Prime+Probe comprises three main steps. In the first step, the entire cache is filled with attacker's data. This step is often referred to as priming the cache. Then, in the second step, the victim encrypts some plaintext **p** which causes partial eviction of the data the adversary has filled in the cache with. In the third step, the adversary analyzes which cache parts have been evicted by the victim's encryption by measuring its own access times to the respective cache parts. This measurement step is called a "probe" step. To conduct the timing measurements the attacker reloads the same data into the cache as in the first step, but carefully observes how much time it takes. Analogously to Evict+Time, longer access times indicate cache evictions whereas shorter access times suggest that the victim has not touched the corresponding cache parts. Having collected the cache access time data, the attacker correlates them to cryptographic algorithms structure and tries to extract confidential information.

Prime+Probe comprises three main steps, as summarized below.

- 1. Attacker primes parts of the cache.

- 2. Victim process accesses or does not access the respective cache parts.

- 3. Attacker probes the same parts of the cache and measures the time for retrieving the data.

Prime+Probe was originally leveraged to abuse the core-private cache to leak confidential information, but in the last decade also approaches targeting at exploiting the LLC were proposed ,e.g., [Liu+15]. These approaches significantly increase the relevance of Prime+Probe, as they enable the cross-core exploits which makes their success less dependent of the CPU scheduling.

### 2.3.2 Shared Memory and Side-Channel Attack Approaches

Another class of cache-based side-channel attacks relies on the usage of memory pages shared between the attacker and the victim. Although such a requirement is restricting the applicability of these attacks, it is often fulfilled. The operating systems and virtual machine monitors strive for efficient memory management, and apply different optimization techniques. Among them is memory deduplication, also referred to as content-based page sharing, which is applied to reduce the overall memory footprint. This is achieved by merging memory pages with identical content within the same physical machine or across virtual machines. For example, virtual machines running on the same physical host might use identical operating system and/or libraries which increases their potential for memory deduplication. This technique has the potential to achieve significant memory optimization. Gupta et al., for instance, built an extension for the Xen virtual machine monitor to make use of different memory deduplication mechanisms and reported substantial memory savings in [Gup+o8].

Due to its potential for optimization, memory deduplication is applied by a number of hypervisors and operating systems. For instance, Linux leveraged a module called KSM to find equal pages in the system [AEWo9]. This module allows for sharing pages across different processes and KVM virtual machines. VMWare also applied a set of techniques to eliminate redundancy in memory and reduce the copying overheads [Walo2]. Due to its advantages most known operating systems and hypervisors make use of deduplicating memory.

However, along with the benefits it provides, page sharing among mutually untrusted processes exposes the involved processes to security risks and reveals new security threats [Bos+16; Suz+11]. Thus, it creates just another trade-off between memory optimization and security. Moreover, according to an empirical study conducted by Chang et al. and described in [CWL11], memory deduplication provides much less optimizations as previously reported. Chang et al. argue that the absolute sharing levels (which exclude zero pages) typically remain under 15%. At the same time, the memory sharing poses a serious security threat to the systems. Bosman et al. conducted a powerful attack against the Microsoft Edge browser [Bos+16], which was reported as a vulnerability CVE-2016-3272, and addressed by Microsoft by changing the defaults regarding the memory deduplication usage. VMWare also reacted to the security threat related to memory deduplication and changed the default settings for Transparent Memory Sharing [VMwb]. Among the strategies that exploit page sharing are Flush+Reload and Flush+Flush.

#### 2.3.2.1 *Flush+Reload*.

Flush+Reload is an attack strategy proposed by Yarom et al. [YF14] in which an adversary exploits the ability to monitor victim's accesses to shared memory pages, which can be applied in a virtualized environment. The attack targets at the LLC cache which makes it a powerful mechanism to leak information cross-cores, i.e., it is independent of the co-location of the attacker and the victim on the same CPU core.

Flush+Reload is based on the observation that whenever a process accesses a shared page in memory, the accessed data is cached. Once the data has been cached, the attacker evicts deliberately chosen and monitored memory locations from the cache using the flush instruction (e.g., clflush). By repeatedly reloading the same data and measuring the time it takes for accessing them, the attacker infers whether the victim has accessed it in the meanwhile or not.

The abstract steps involved in a Flush+Reload attack are summarized below.

- 1. The adversary flushes a deliberately chosen memory location.

- 2. The victim performs operations.

- 3. The adversary access the same memory location again and measures the time.

The applicability of the attack proposed by Yarom et al. to the LLC increases its significance, as it enables an attacker to monitor the victim from another CPU core.

#### 2.3.2.2 *Flush+Flush*.

Flush+Flush, proposed by Gruss et al. in [Gru+16], is an extension of the Flush+Reload attack, but it leverages only the timing variation of the flush instruction itself and is not reliant on the memory accesses.

Hence, Flush+Flush attacks are harder to detect by mechanisms analyzing the memory accesses and are considered more robust against detection mechanisms.

#### 2.4 SYSTEM AND ATTACKER MODELS

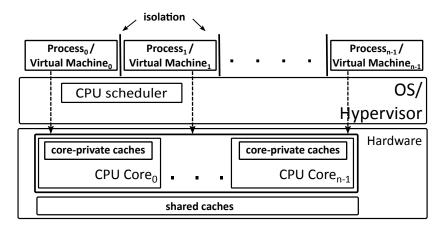

This section details the system model that underlies this thesis. The presented system model is an abstraction of the system models applied in the individual contributions of the thesis. All of the contributions are focused on the cache as a side channel and consist of a hardware part comprising the CPU cores along with the different cache levels. It includes the core-private cache (i.e., L1 cache) and shared caches (e.g., LLC).

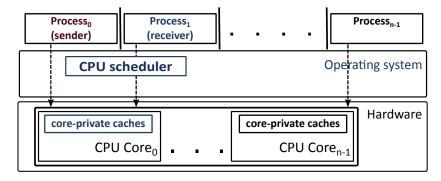

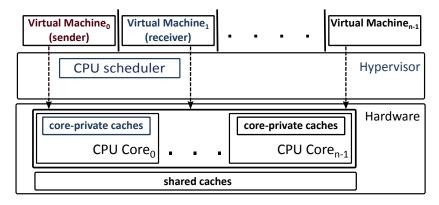

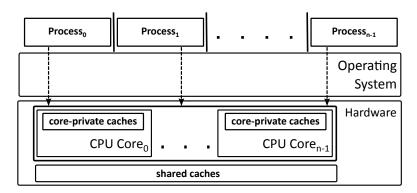

Depending on the contribution, either a hypervisor, called also virtual machine monitor (VMM), or an operating system (OS) runs on top of the hardware. The hypervisor is a software layer, which is a part of each virtualization solution and enables the multiplexing of tenants or users encapsulated in virtual machines on the same physical machine. A virtualized environment is characterized by providing a low-level abstraction from the hardware state. Both in the cases of an underlying hypervisor or OS, a secure isolation between the running virtual machines (in the case of a hypervisor) or between the processes (in the case of an OS) is presumed. The abstract system model is depicted in Figure 3.

Any attacker processes considered in this thesis is assumed to have control over non-privileged processes or virtual machines running on the system. The attacker(s) can indirectly manipulate the cache in the way any user-land process can do by accessing data or instructions. Attackers with privileged access to the system, such as the one described in [Bra+17], which can manipulate the

Figure 3: Abstract System Model.

performance counters, but cannot read victim's memory directly, are out of the scope of the thesis.

# Part II

ON THE CLASSIFICATION, FEASIBILITY AND MODELING OF SIDE-CHANNEL ATTACKS

# TOWARDS THE SYSTEMATIC REASONING ABOUT SIDE-CHANNEL ATTACKS

Millen defined four major research areas considering the side channels: (i) explaining, (ii) finding, (iii) measuring and (iv) mitigating side channels in [Mil99]. The objective of this chapter is to enable systematic reasoning about the side-channel attacks considering their execution environment which covers the explanation field, but is also connected to the rest of the defined research areas. The content of this chapter is, partly verbatim, based on material from [Vat+14a; Vat+14b] and tackles the first contribution of the thesis (cf., Section 1.3).

This chapter is organized as follows. Section 3.1 presents the motivation for this contribution. Section 3.2 gives an overview on a proposed generic classification approach. Section 3.3 focuses on feasibility factors that affect the exploits of the cache side effects in a virtualized environment. The related work is presented in Section 3.4, and the concluding remarks are given in Section 3.5.

#### 3.1 CLASSIFICATION AND FEASIBILITY ENDEAVOURS

The term side channel denotes a communication channel that stems from the usage of shared resources and can be exploited, e.g., through manipulations or observations. As the traditional intrusion detection systems are not tailored to protect from such exploits, mainly due to the nature of the side channels, side-channel attacks are considered a serious threat for compromising the confidentiality within diverse execution environments. At the same time, with the advent of Cloud computing, the side-channel attacks relevance has even increased due to the intrinsic sharing of resources across security boundaries, which has led to a higher number of reported side-channel attacks (cf., Figure 1).

While these attacks represent a real threat to the security of any system, almost each manifestation of the attacks is commonly only successful given certain pre-requisites or fulfilling certain assumptions. To better understand the side-channel threat and the feasibility of a specific attack, given the huge number of existing side-channel exploits, a generic classification that takes into account the specifity of the execution environment and the attack assumptions is needed. The lack of a generic side-channel attacks classification approach that encompasses both the type of exploit and the execution environment factors affecting its success impedes the systematic analysis of the side-channel attacks threat and the assessment of their feasibility. Such a classification approach has to take into account not only native, but also virtualized environments.

The term virtualization has been present in the IT community for a long time starting from the late sixties [PG74] until now, and has undergone periods of less popularity to gain significance again during the last decades [FDF05]. Despite the presumed strong logical isolation that virtualization provides, virtualized environments and systems offering shared resources or relying on virtualization (e.g., the Cloud) are vulnerable to side-channel exploits due to the inherent resource sharing among mutually untrusted customers. To address the security concerns regarding the side-channel attack threat, VMWare changed their hypervisor default settings following the demonstration of side-channel attacks which exploit memory deduplication [VMwb]. Amazon EC2 Dedicated Instances model also provides services dedicated explicitly to a single customer [Ama14]. This strongly emphasizes the efforts of not only the academic, but also the industrial world to address the concerns related to the side-channel attacks, especially in virtualized environments.

However, the security provided by such solutions comes at a price. Not using memory deduplication or using dedicated instances for a single customer potentially results in a worse utilization of resources which can increase the price of the services for the end users. Therefore, it would be beneficial to assess the feasibility of side-channel attacks by considering the specific execution context of a virtualized environment. Such an environment, multiplexing users on the same resource, exhibits characteristics specific to the virtualization technology. Hence, the side-channel exploits feasibility in a virtualized environment does not necessarily overlap with their feasibility in a native environment. Therefore, considering feasibility aspects in a virtualized environment is needed, as it can aid research on the virtualization isolation strength, and the actual countermeasures to mitigate specific side-channel attacks based on the execution environment and their assumptions.

Among the objectives of the thesis is to investigate the side-channel attack types and to determine the conditions under which these exploits are feasible considering the specific execution environment. For this purpose, we propose a generic classification to serve as a basis for the comparison and analysis of side-channel attacks (SCAs) with respect to diverse characteristics. An extensive classification approach comprising various attack aspects can facilitate the easier identification of mitigation paths for a specific context and of protection mechanisms which can be applied to decrease the probability of such an exploit. This extends the research on side-channel attacks classifications which typically does not focus on the execution environment impact and does not investigate under which conditions a specific attack can be conducted and is feasible.

The feasibility of a certain attack always depends on the adopted means, and we do not claim to provide absolute statements about attacks feasibility, but we aim to provide information regarding the conditions under which specific types of attacks are more or less probable. For this purpose, a selection of demonstrated side-channel exploits in a virtualized environment is considered.

#### 3.2 SIDE-CHANNEL ATTACKS CLASSIFICATION APPROACH

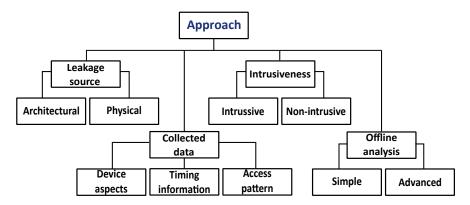

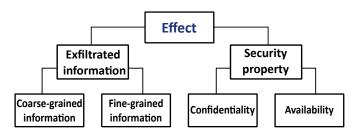

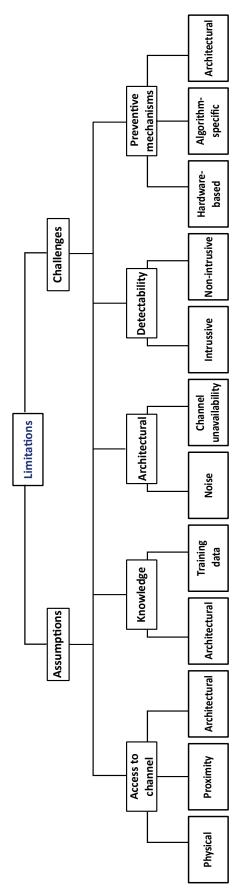

We classify existing side-channel attacks to facilitate the assessment of the security-related properties of the execution environment in which these exploits can be conducted. For this, we define three main categories to characterize an attack according to the: (i) approach, (ii) effect and (iii) limitations. An overview on the proposed classification is given in Figure 4, and the subsequent paragraphs provide a detailed explanation regarding the different classes. In this section, we argue that attack's important characteristics are derived from the way it is conducted with a focus on the effect it has on the exploited system and its potential for success. However, the contextual limitations of the attack in terms of assumptions and challenges may not be neglected to truly excel in studying the details of the exploit.

Figure 4: Overview of the Classification Approach.

## 3.2.1 Approach

The approach category describes the adversary strategy, i.e., the way the adversary compromises the security of a system by exploiting a side channel. We differentiate the side-channel attacks further depending on the leakage source or the shared medium being used for conducting the attack, on the intrusiveness of the attack, on the type of the collected and analyzed measurements and the method applied for analyzing the gathered data. This categorization is shown in Figure 5.

Figure 5: Detailed Overview of "Approach".

Figure 6: Detailed Overview of "Effect".

## 3.2.1.1 Leakage source

We further refine the classification by categorizing the side-channel attacks into physical attacks and architectural attacks in terms of the leakage medium or leakage source that has been leveraged for conducting the attack. The architectural side-channel attacks make use of an architectural system component. Such examples include the L1 cache, exploited as a side channel [Zha+12], the L2 cache [Xu+11], the L3 cache [YF14], virtual memory paging [Pero5], etc. The physical side-channel attacks, in turn, exploit device components to conduct the attack, e.g., keyboard, monitor, power supply unit, etc. Examples of attacks that leverage the power supply unit are given in [Hla+11; MDS99].

#### 3.2.1.2 Collected data

Depending on the type of the collected data, we distinguish between exploits leveraging physical device aspects, exploits measuring timing information and exploits relying on the characteristics of the access patterns to the side channel.

PHYSICAL DEVICE ASPECTS. This category encompasses attacks observing physical device aspects, such as power consumption, needed for the conduct of the attacks [Hla+11; MDS99], electromagnetic emanations, used for the attacks [Agr+03; Car+04], acoustic emanations, analyzed for the attacks in [GST14; SWT01]. These device characteristics are monitored and collected while the respective physical device performs a sensitive operation, for instance during cryptographic encryption.

TIMING INFORMATION. Timing information provides the basis for conducting attacks known as time-driven attacks. Sometimes, time-driven attacks have coarse granularity of the observations and are more successful if the time needed for the sensitive operation of attacker's interest (e.g., encryption process) is known in advance. To enable the statistical inference of information, the measurements might have to be conducted repeatedly. An attack relying on timing information is described in [Kocg6].

ACCESS PATTERN. Information regarding the accesses to the side channel is leveraged to conduct access-driven attacks. A representative example for this kind of attacks are exploits leveraging the cache as a side channel, but the access

patterns also to other shared architectural assets can be used to leak information. Very often this attack type involves collecting time measurements, but they are only used to deduce the access pattern to the observed shared resource. Depending on the specific attack, the involved timing measurements might not necessarily be of very high granularity. Examples of this category are the attacks described in [Pero5; Ris+09; WXW12; Xu+11; YF14; Zha+12].

## 3.2.1.3 Intrusiveness

Another important characteristic of the side-channel exploits is their intrusiveness. We differentiate between intrusive and non-intrusive attacks.

INTRUSIVE. A prerequisite for the intrusive side-channel attacks is the direct access to the internal components of the observed device. Adversaries performing intrusive side-channel attacks intervene with device operation.

NON-INTRUSIVE. The non-intrusive side-channel attacks, on the contrary, are passive attacks and only monitor the device operation without intervening with it. Only externally available information, which has not been intentionally leaked, is leveraged in this case. Representative examples for this type of attacks are given in [Agr+03; GST14; Koc96; Ris+09; SWT01; YF14].

## 3.2.2 Offline analysis

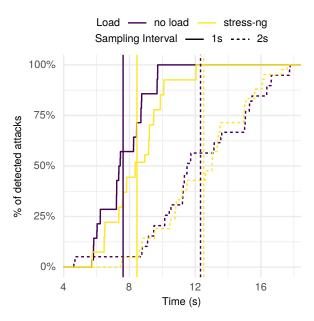

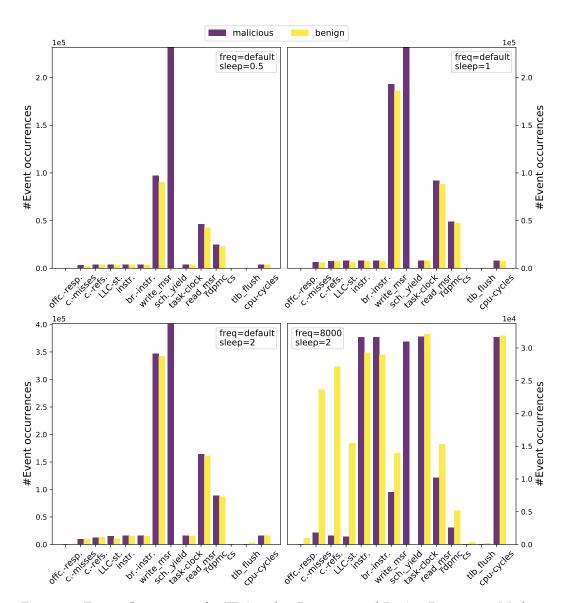

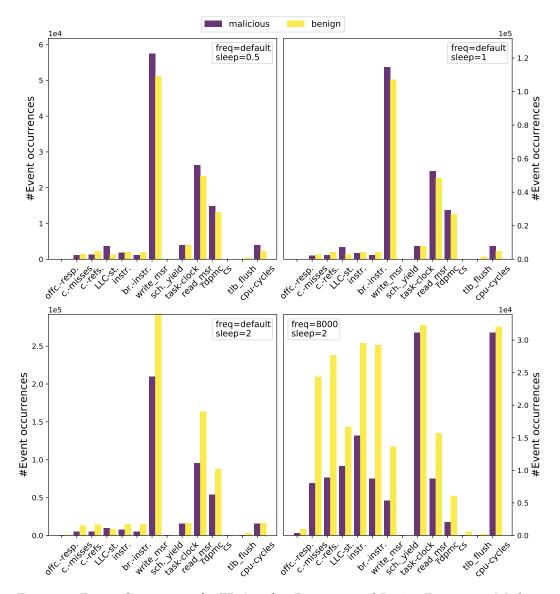

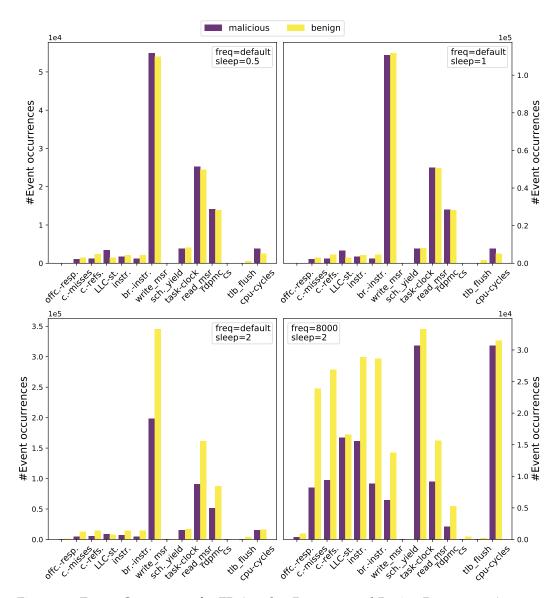

The way the collected data is analyzed after the measurements have been conducted (i.e., offline), is used to further refine the proposed classification. We differentiate between advanced side-channel attacks and simple side-channel attacks, as already proposed in [ZDo5].